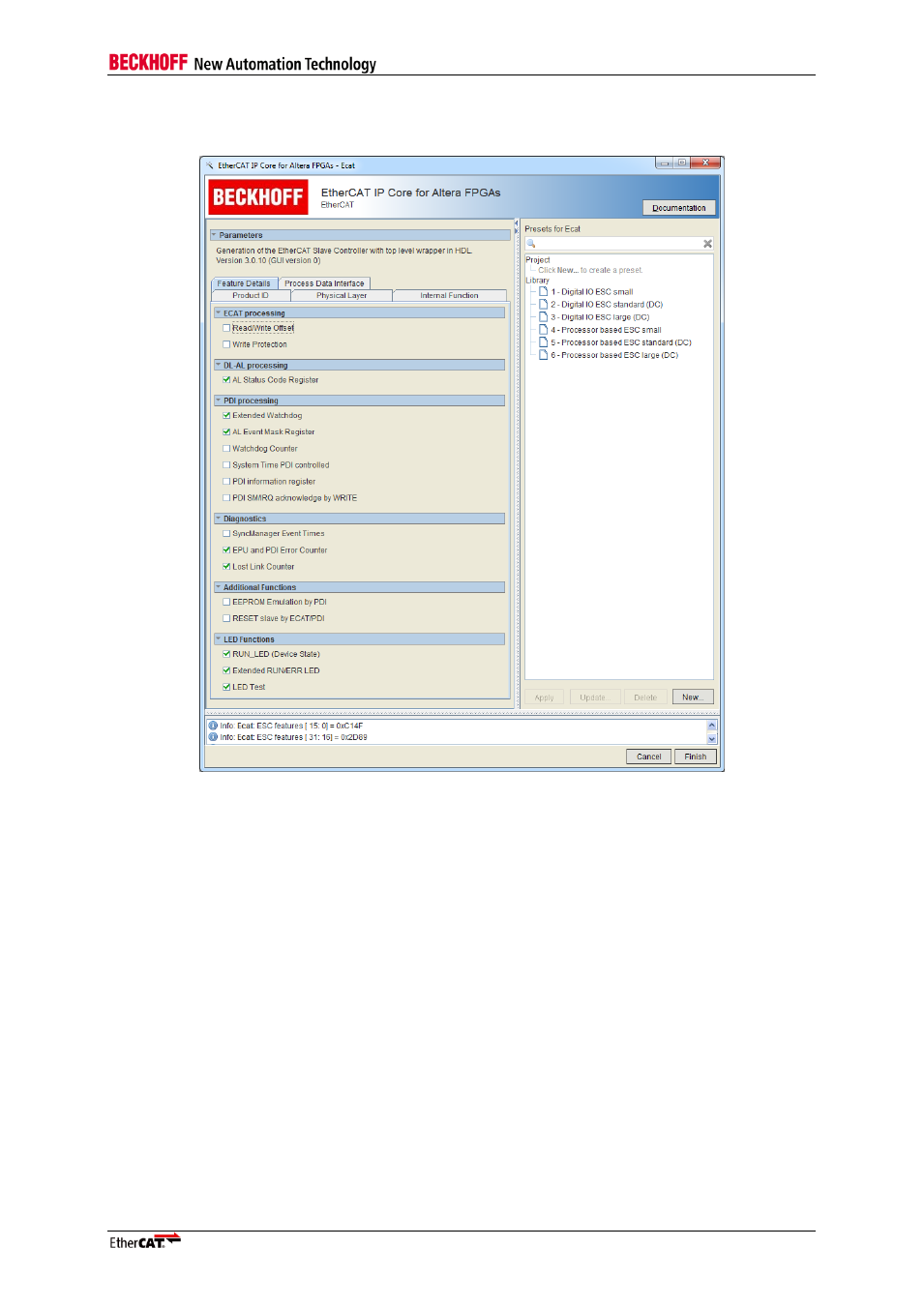

4 feature details tab, Feature details tab, Figure 12: feature details tab – BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 51

IP Core Configuration

Slave Controller

– IP Core for Altera FPGAs

III-39

5.2.4

Feature Details tab

Figure 12: Feature Details tab

Read/Write Offset

Physical Read/Write Offset (0x00108:0x0109) is available if checked.

Write Protection

Register write protection and ESC write protection (0x0020:0x0031) are available if checked.

AL Status Code Register

AL Status Code register (0x0134:0x0135) is available if checked.

Extended Watchdog

Watchdog Divider (0x0400:0x0401) is configurable and PDI Watchdog (0x0410:0x0411, and

0x0100.1) is available if checked.

AL Event Mask Register

AL Event Mask register (0x0204:0x0207) is available if checked.

Watchdog Counter

Watchdog Counters (0x0442:0x0443) are available if checked. Watchdog Counter PDI is only used if

Extended Watchdog feature is selected.

System Time PDI controlled

Distributed Clocks Time Loop Control Unit is controlled by PDI (µController) if selected. EtherCAT

access is not possible. Used for synchronization of secondary EtherCAT busses.