7 fpga resource consumption, Fpga resource consumption – BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 69

FPGA Resource Consumption

Slave Controller

– IP Core for Altera FPGAs

III-57

7

FPGA Resource Consumption

The resource consumption figures shown in this chapter reflect results of example synthesis runs and

can only be used for rough resource estimations. The figures are subject to quite large variations

depending on design tools and version, FPGA type, constraints (e.g., area vs. speed), total FPGA

utilization (design tools typically stop optimization if the timing goal is reached), etc. No extra effort

was undertaken to achieve optimum results, i.e. by sophisticated constraining and design flow setting.

For accurate resource consumption figures, please use the evaluation license of the EtherCAT IP

Core and synthesize your individual configuration for the desired FPGA.

The figures of the following table do not imply that the individual features are operational in the

selected FPGA (i.e., that the resources are sufficient or that timing closure is achievable). The

synthesis runs where performed without timing constraints, without location constraints, and without

bitstream generation.

The EtherCAT IP core resource consumption overview figures are based on EtherCAT IP Core for

Altera FPGAs Version 3.0.2, Altera Quartus II 12.1 SP1, and Altera Cyclone IV devices.

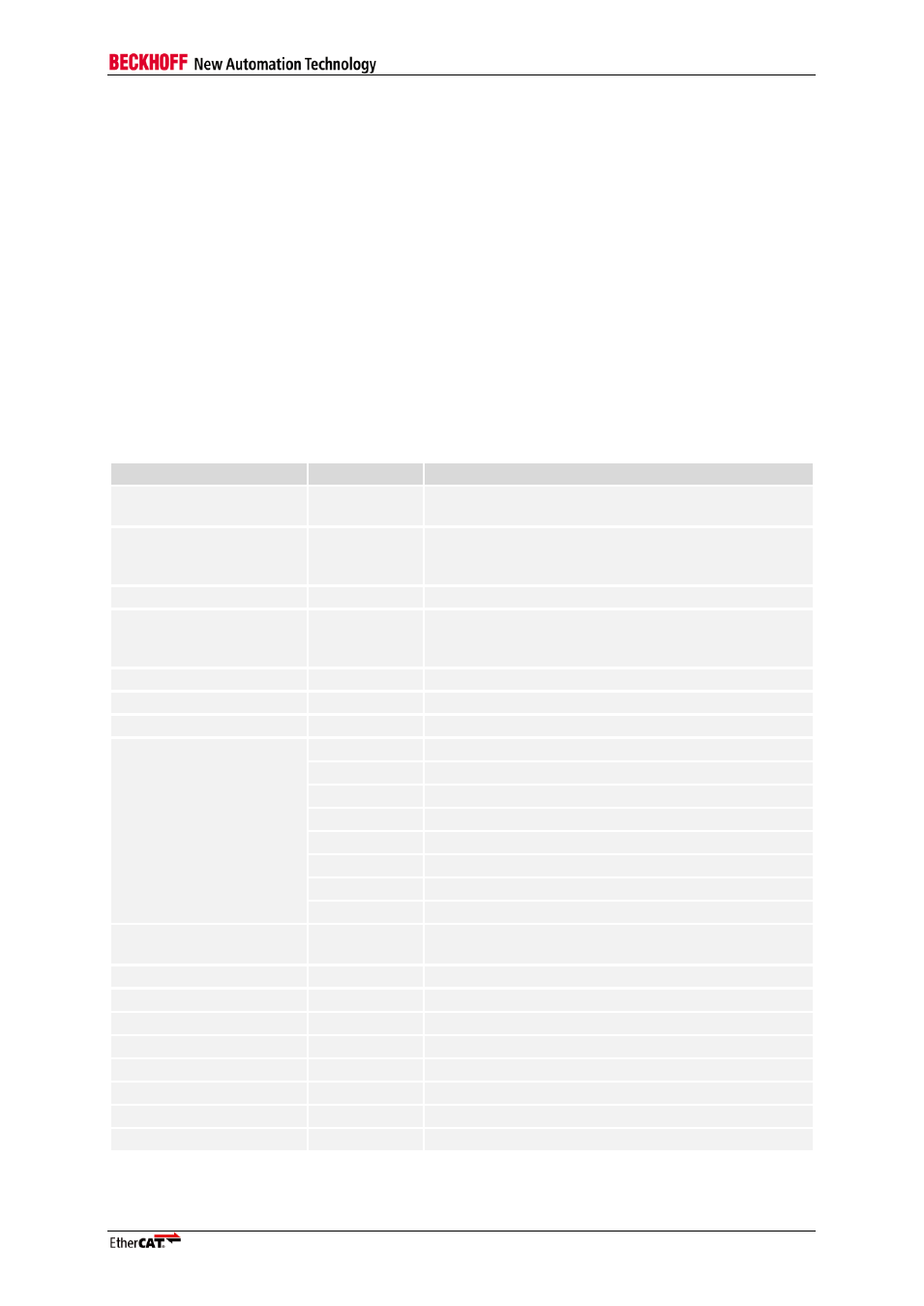

Table 17: Typical need of Logic Cells (LE) for main configurable functions

Configurable Function

Approx. LE

Details

Minimum Configuration

3,850

0 x SM, 0 x FMMU, no features, no DC, PDI: 32 Bit

digital I/O, 1 kByte DPRAM, 1 port MII

Maximum Configuration

32,500

8 x SM, 8 x FMMU, all features except for EEPROM

Emulation, DC 64 bit, PDI: SPI, GPIO, 60 kByte

DPRAM, 3 ports MII

Additional port

1,200

all port features enabled (without DC Receive time)

PHY features

950

All MII features: Management Interface, MI link

detection and configuration, TX Shift, and enhanced

link detection (3 ports)

SyncManager

1,100

per SyncManager

FMMU

700

per FMMU

DPRAM

500

60 KB (M4K/M9K)

Distributed Clocks

200

Receive time per port

1,300

System time (32 bit)

1,800

SyncSignals (32 bit)

750

LatchSignals (32 bit)

1,800

System time (64 bit)

3,400

SyncSignals (64 bit)

1,300

LatchSignals (64 bit)

350

SyncManager Event Times

Feature details

800

all features except for EEPROM Emulation and DC

Receive time

PDI

32 Bit Digital I/O

1,150

SPI

2,400

8 Bit µController

1,750

16 Bit µController

2,300

Avalon

1,700

25 MHz, 32 Bit

AXI

2,800

25 MHz, 32 Bit

GPIO

550

8 Byte