BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 80

IP Core Signals

III-68

Slave Controller

– IP Core for Altera FPGAs

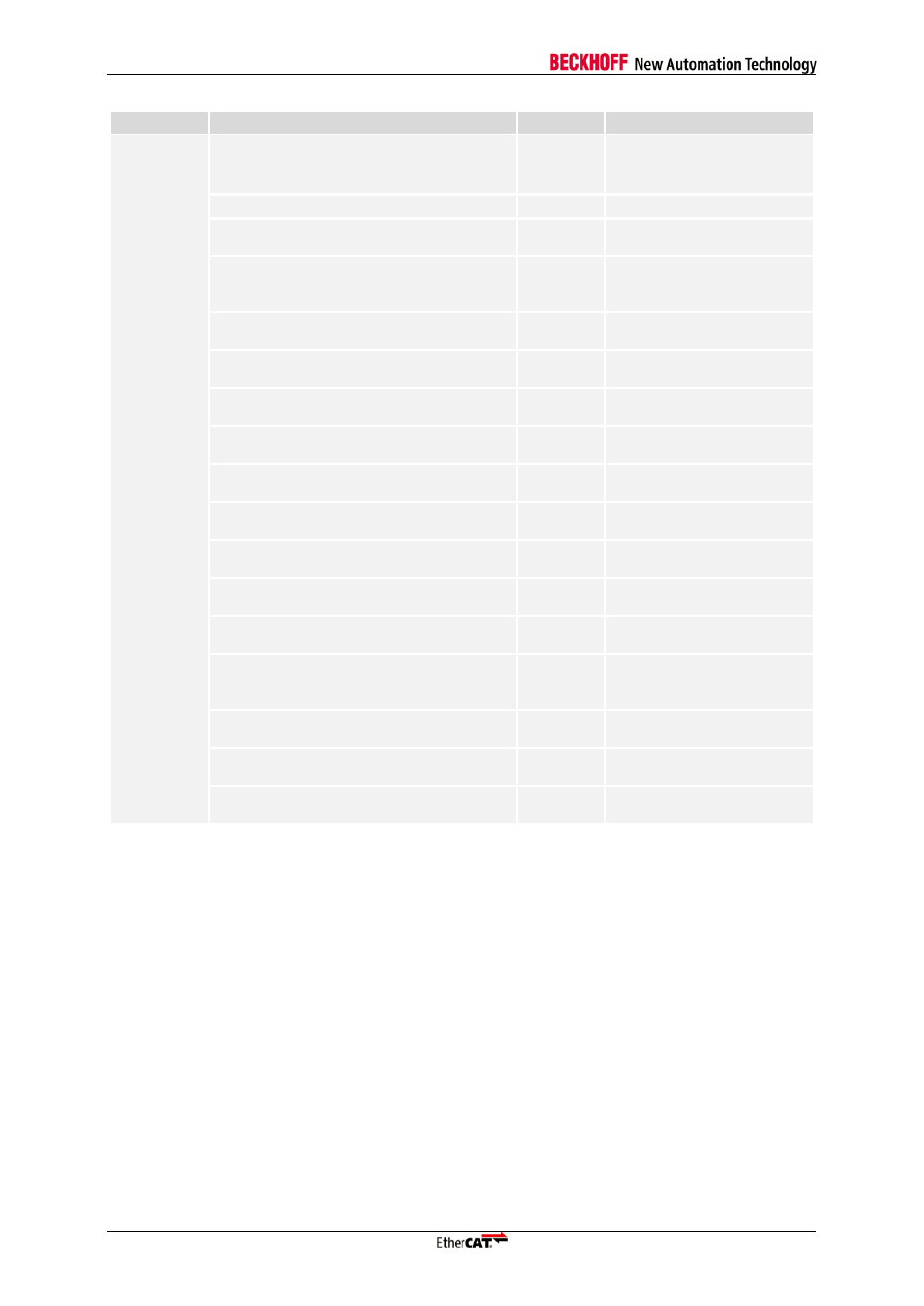

Condition

Name

Direction

Description

Port1 =

RGMII

nRGMII_LINK1

INPUT

0: 100 Mbit/s (Full

Duplex) link at port 1

1: no link at port 1

RGMII_RX_CLK1

INPUT

Receive clock port 1

RGMII_RX_CTL_DATA_DDR_CLK1

OUTPUT

Receive control/data DDR

input clock port 1

RGMII_RX_CTL_DATA_DDR_NRESET1

OUTPUT

Receive control/data DDR

input reset (port 1, act.

Low)

RGMII_RX_CTL_DDR_L1

INPUT

Receive control DDR input

low port 1

RGMII_RX_CTL_DDR_H1

INPUT

Receive control DDR input

high port 1

RGMII_RX_DATA_DDR_L1

INPUT

Receive data DDR input

low port 1

RGMII_RX_DATA_DDR_H1

INPUT

Receive data DDR input

high port 1

RGMII_TX_CLK_DDR_CLK1

OUTPUT

Transmit clock DDR output

clock port 1

RGMII_TX_CLK_DDR_NRESET1

OUTPUT

Transmit clock DDR output

reset (port 1, act. Low)

RGMII_TX_CLK_DDR_L1

OUTPUT

Transmit clock DDR output

low port 1

RGMII_TX_CLK_DDR_H1

OUTPUT

Transmit clock DDR output

high port 1

RGMII_TX_CTL_DATA_DDR_CLK1

OUTPUT

Transmit control/data DDR

output clock port 1

RGMII_TX_CTL_DATA_DDR_NRESET1

OUTPUT

Transmit control/data DDR

output reset (port 1, act.

Low)

RGMII_TX_CTL_DDR_L1

OUTPUT

Transmit control DDR

output low port 1

RGMII_TX_CTL_DDR_H1

OUTPUT

Transmit control DDR

output high port 1

RGMII_TX_DATA_DDR_L1

OUTPUT

Transmit data DDR output

low port 1