4 ip core usage, 1 ip catalog, 2 qsys – BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 43: Ip core usage, Ip catalog, Qsys, Figure 6: qsys with ethercat ip core

IP Core Usage

Slave Controller

– IP Core for Altera FPGAs

III-31

4

IP Core Usage

4.1

IP Catalog

The EtherCAT IP Core is integrated in the Quartus II IP Catalog, you can add it to your Quartus II

project like any other IP and configure it with the MegaWizard.

The output of the MegaWizard is a VHDL or Verilog wrapper for the EtherCAT IP Core. The wrapper

file makes only those signals and interfaces visible, which are required, and it configures the

EtherCAT IP Core using generics as desired.

A synthesizable EtherCAT IP Core consists of the user generated VHDL wrapper, the encrypted

EtherCAT IP Core files, and the vendor ID package (ECAT_VENDORID.vhd). These files, together

with a PLL, represent the minimum source set for a fully functional EtherCAT slave. Typically,

additional user logic is added inside the FPGA.

4.2

Qsys

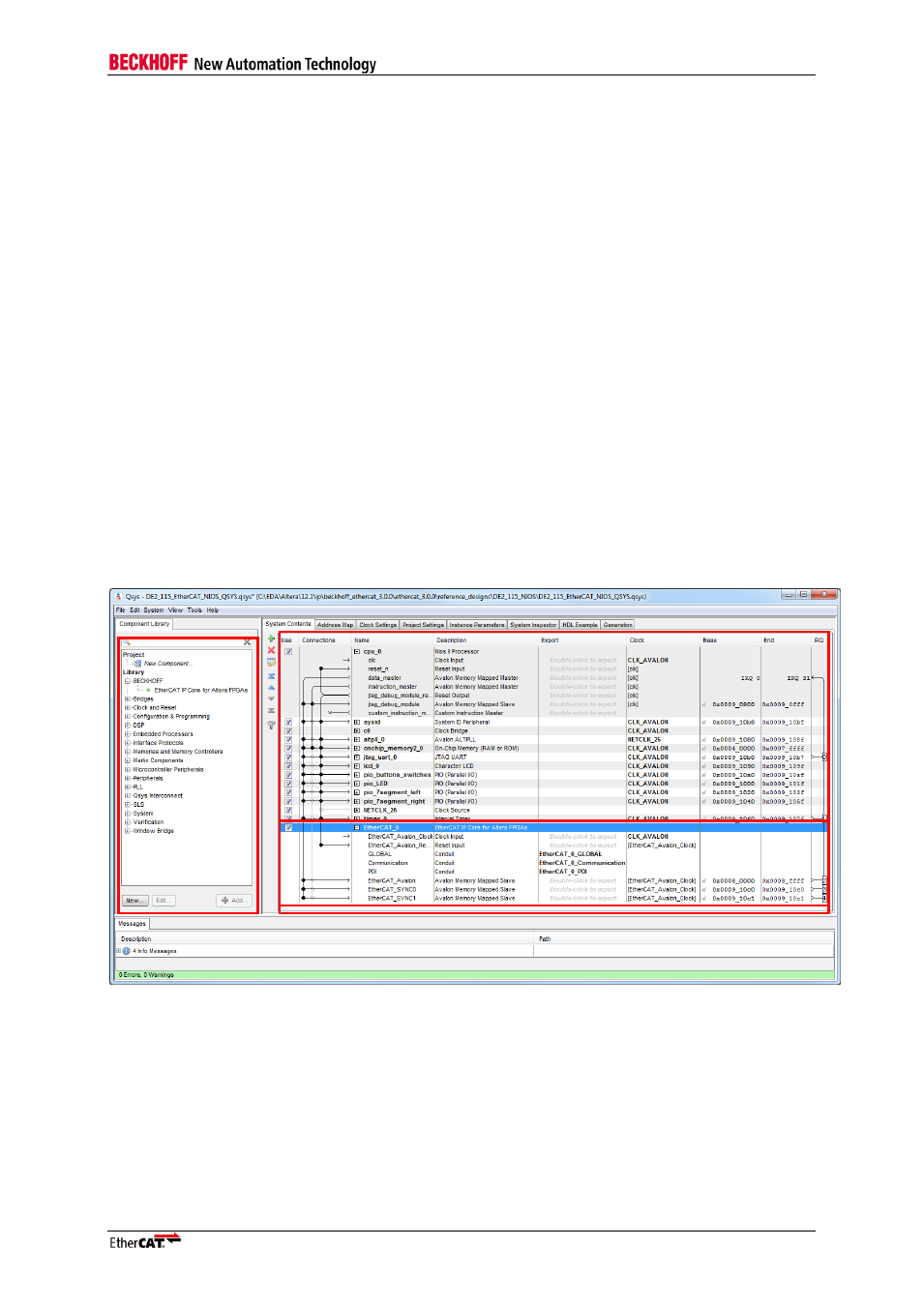

The EtherCAT IP Core can also be integrated into a System on a Programmable Chip (SoPC) with a

processor inside the FPGA (e.g., Altera NIOS II processor). The EtherCAT IP Core and the processor

can communicate via an Avalon or AXI3 on-chip bus system.

For building an SoPC including the EtherCAT IP Core, Altera Qsys is used (Figure 6). The NIOS

processor and the EtherCAT IP Core as well as other resources which might be used for an SOPC are

listed under the System Resources (Figure 6). Signal Routing is done automatically. The interrupts

used by the EtherCAT IP Core (Avalon_ethercat_sync0, Avalon_ethercat_sync1, and PDI collector

interrupt Avalon_ethercat_slave) are listed and signal routing is shown.

Figure 6: Qsys with EtherCAT IP Core

System

Resources

System Configuration

EtherCAT

IP Core