13 electrical specifications, Electrical specifications, Table 65: ac characteristics – BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 136: Table 66: forwarding delays

Electrical Specifications

III-124

Slave Controller

– IP Core for Altera FPGAs

13 Electrical Specifications

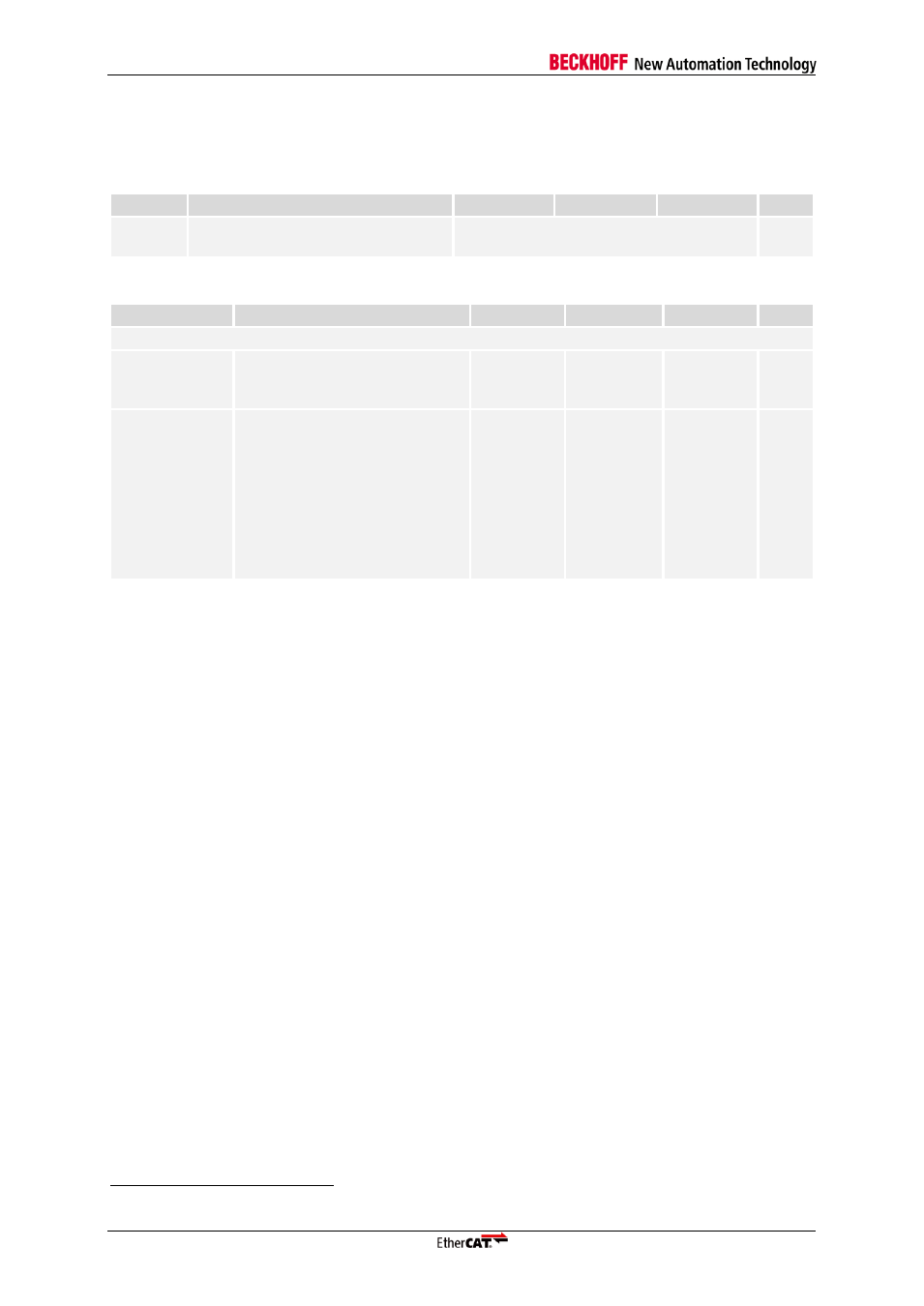

Table 65: AC Characteristics

Symbol

Parameter

Min

Typ

Max

Units

f

CLK25

Clock source (CLK25) with initial

accuracy

25 MHz ± 25 ppm

Table 66: Forwarding Delays

Symbol

Parameter

Min

Average

Max

Units

PRELIMINARY TIMING

t

Diff

Average difference processing

delay minus forwarding delay

(without RX FIFO jitter)

40

ns

t

MM

MII port to MII port delay:

a) Through ECAT Processing

Unit (processing)

b) Alongside ECAT Processing

Unit (forwarding)

Conditions: FIFO size 7, no TX

Shift compensation or manual

TX Shift configuration with

MII_TX_SHIFT = 00

a) 300+x

14

b) 260+x

a) 320+x

b) 280+x

a) 340+x

b) 300+x

ns

NOTE: Average timings are used for DC calculations.

14

EtherCAT IP Core: time depends on synthesis results