5 process data interface tab, Process data interface tab, Figure 13: available pdi interfaces – BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 53

Advertising

IP Core Configuration

Slave Controller

– IP Core for Altera FPGAs

III-41

5.2.5

Process Data Interface tab

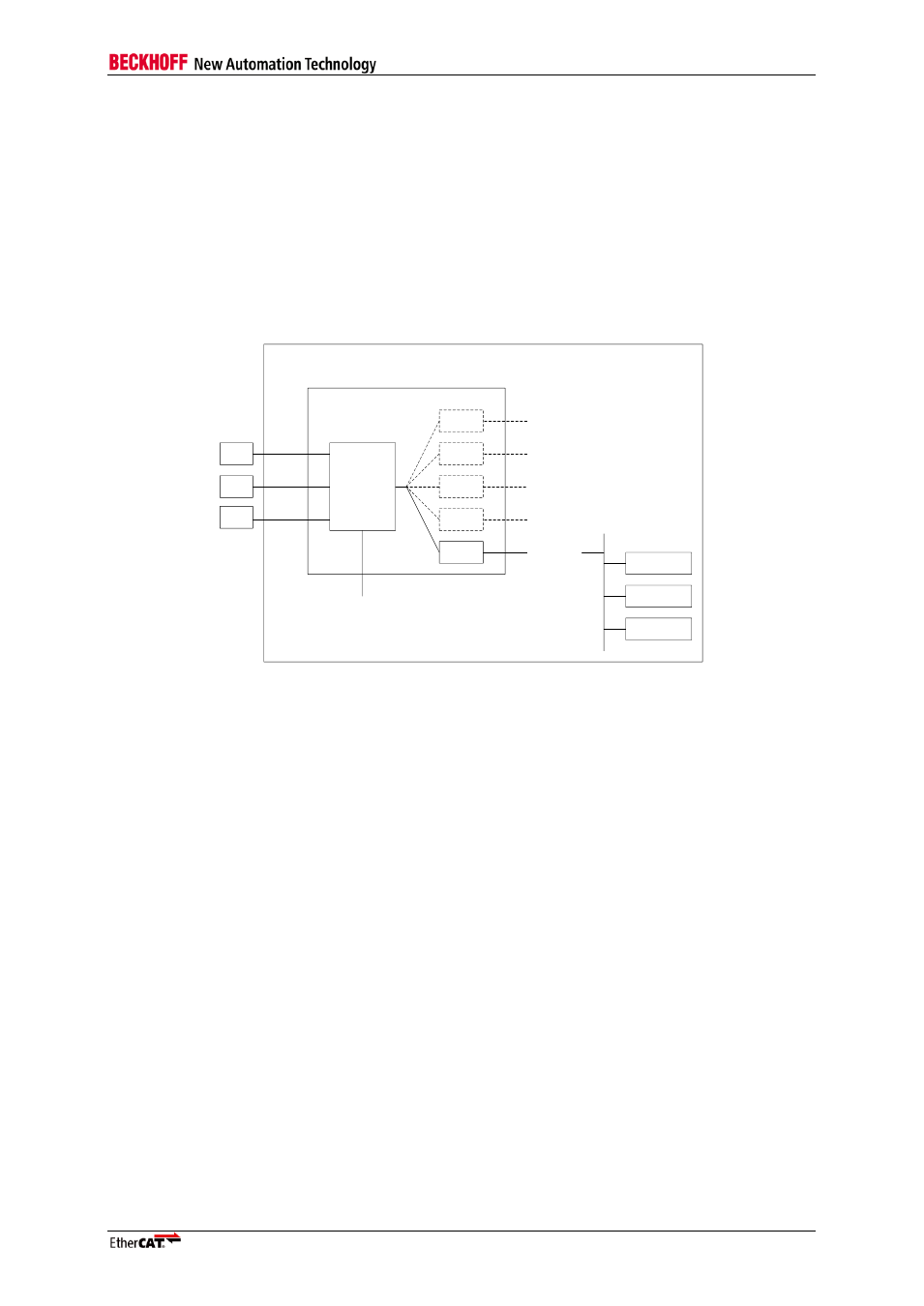

Several interfaces between ESC and the application are available:

Digital I/O

8 Bit asynchronous µController

16 Bit asynchronous µController

SPI slave

Avalon MM slave

AXI3 slave

General Purpose I/O

EtherCAT

Logic

PDI

PDI

PDI

PDI

SPI

Digital I/O

µC 8 Bit

Avalon/

AXI

EtherCAT IP Core

NIOS

RAM

…..

µC 16 Bit

PDI

FPGA

PHY

PHY

PHY

General

Purpose I/O

Figure 13: Available PDI Interfaces

The PDI can be selected from the pull down menu. After selection settings for the selected PDI are

shown and can be changed. If the EtherCAT IP Core is used in Qsys, only Avalon and AXI on-chip

busses are selectable.

Advertising