8 design flow, Design flow, Figure 3: design flow – BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 25

Advertising

Overview

Slave Controller

– IP Core for Altera FPGAs

III-13

1.8

Design flow

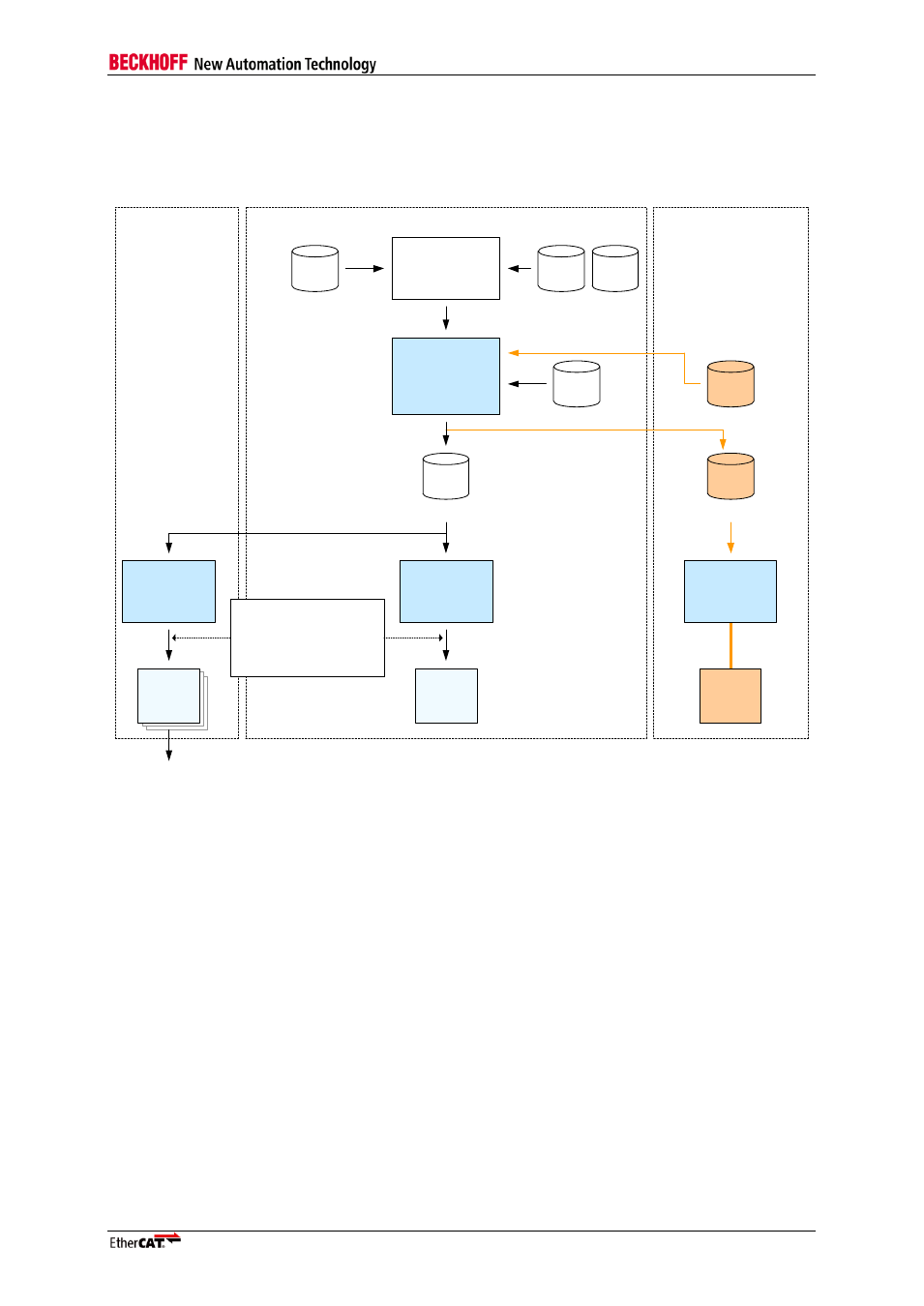

The design flow for creating an EtherCAT Slave Controller based on the EtherCAT IP Core is shown

in the following picture:

Synthesis

User logic

License file (full)

FPGA configuration file

Download

utility

FPGA

Buy-out license /

Quantity-based license

(license agreement)

grants permission

Evaluation

Development

Download

utility

MAC ID

Dongle

bit-

stream

Application

specific ESC

sources

VHDL

Verilog

Schematic

Production

FPGA

FPGA

Download

utility

FPGA

FPGA configuration file

bit-

stream

(OpenCore Plus)

FPGA

(OpenCore Plus)

IP Core

installation

encrypted

VHDL

Customer

License file (eval)

MAC ID

Dongle

or

Vendor

ID

JTAG

tethered

(else timebomb)

Vendor ID

package

Figure 3: Design flow

Advertising