Igure, Fxo/dpt v, Oice – Verilink XEL XSP-100 SHARK IAP (9SA-USRS-9.0R1.02) Product Manual User Manual

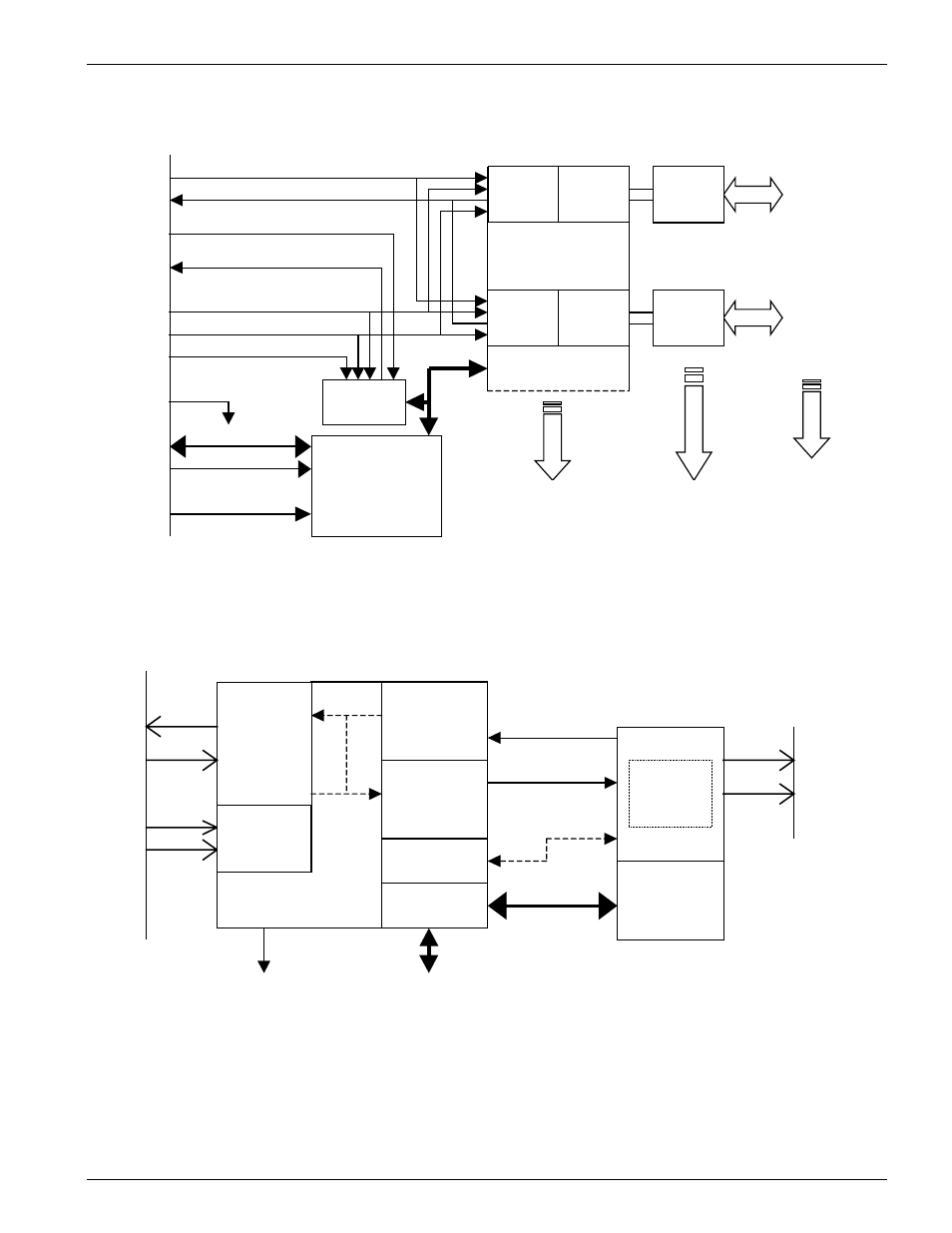

Page 234: Odule, Circuits, Ndividual, Ircuits, Figure 27: fxo/dpt voice module (8 circuits), Figure 28: individual fxo/dpt voice circuits

Chapter 9- Hardware Specifications

Chapter 9-34 XEL P/N & Release: 9SA-USRS-9.0R1.02 SHARK™ IAD User's Guide

Com port (5)

Reset line (2)

MCU

controlling

8 circuits

Tdata (1)

Rdata (1)

Frame Strobe (1)

B

a

c

k

P

l

a

n

e

2 wire

Port A

Channel A

digital

conversion

Termination

+ Voice

adjustments

SLIC

Channel B

digital

conversion

Termination

+ Voice

adjustments

SLIC

2 wire

Port B

2 wire

Port C to H

Control bus

FXO Voice Plug - 8 Circuits

SF Strobe (1)

Plug Slot Location (2)

Rcv data clock (1)

Signaling

interface

SLAC

Rx signaling (1)

Tx signaling (1)

occupied

Figure 27:

FXO/DPT Voice Module (8 circuits)

Ring Lead

Tip Lead

SLIC controls

and sensors

600/ 900 ohm

2/4-wire

hybrid

network

Control bus to/from MCU

PCM

Encoding

Decoding

Interrupt ReQuest to MCU

Tdata

Rdata

Frame

Strobe

B

a

c

k

P

l

a

n

e

2-wire

Port

Connector

Transmit

Voice

compensation

Receive

Voice

compensation

AISN

coefficients

SLIC control

registers

Clock

Time Slot

Assignor

(TSA)

Figure 28:

Individual FXO/DPT Voice Circuits