2 output signal allocations – Yaskawa Sigma-5 Large Capacity Users Manual: Design and Maintenance-Rotary Motors-Mechatrolink-II Communication Reference User Manual

Page 73

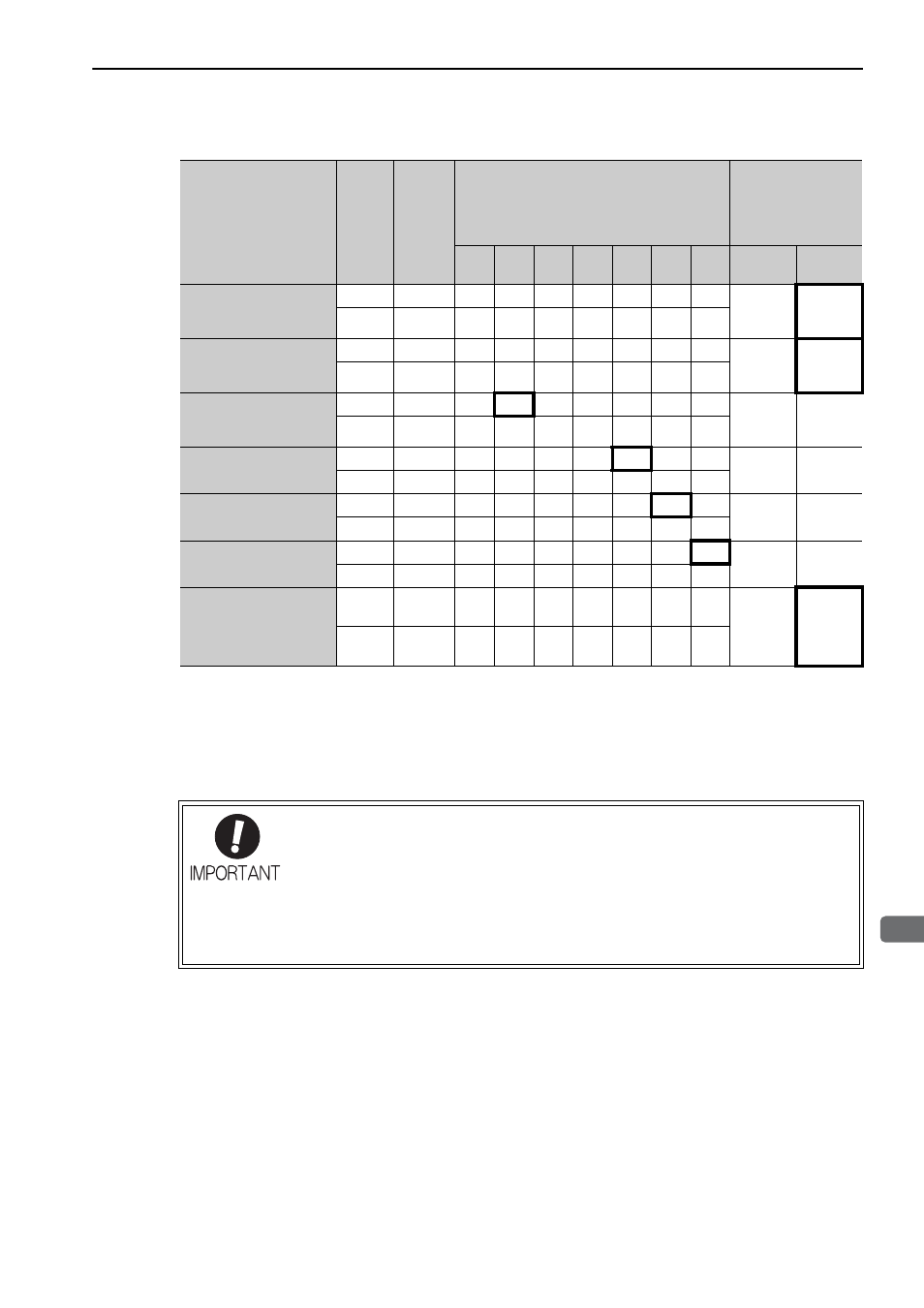

3.4 I/O Signal Allocations

3-27

3

Wi

ring and

C

onne

ctio

n

∗ These pins cannot be used.

Note: The factory settings of the parameters in a large-capacity

Σ-V SERVOPACK are not all the same as those for a stan-

dard

Σ-V SERVOPACK. Make sure that you consider any differences in the factory settings if you copy the param-

eters from a standard

Σ-V SERVOPACK to a large-capacity Σ-V SERVOPACK.

3.4.2 Output Signal Allocations

Output signals are allocated as shown in the following table.

Refer to the Interpreting the Output Signal Allocation Tables and change the allocations accordingly.

<Interpreting the Output Signal Allocation Tables>

Forward External

Torque Limit

Pn50B.2

L

/P-CL

0

1

2

3

4

5

6

7

8

H

P-CL

9

A

B

C

D

E

F

Reserve External

Torque Limit

Pn50B.3

L

/N-CL

0

1

2

3

4

5

6

7

8

H

N-CL

9

A

B

C

D

E

F

Homing Deceleration

LS

Pn511.0

L

/DEC

0

1

2

3

4

5

6

7

8

H

DEC

9

A

B

C

D

E

F

External Latch Signal 1

Pn511.1

L

EXT1

*

*

*

*

4

5

6

7

8

H

/EXT1

*

*

*

*

D

E

F

External Latch Signal 2

Pn511.2

L

EXT2

*

*

*

*

4

5

6

7

8

H

/EXT2

*

*

*

*

D

E

F

External Latch Signal 3

Pn511.3

L

EXT3

*

*

*

*

4

5

6

7

8

H

/EXT3

*

*

*

*

D

E

F

DB Answer

Pn515.2

L

/DBANS

0

1

2

3

4

5

6

7

8

H

DBANS

9

A

B

C

D

E

F

(cont’d)

Input Signal Names

and Parameters

Validity

Level

Input

Signal

CN1 Pin Numbers

Connection Not

Required

(SERVOPACK

judges the connec-

tion)

40

41

42

43

44

45

46

Always

ON

Always

OFF

• The signals not detected are considered as "Invalid." For example, Positioning Com-

pletion (/COIN) signal in speed control is "Invalid."

• Inverting the polarity of the brake signal (/BK), i.e. positive logic, will prevent the hold-

ing brake from working in case of its signal line disconnection.

If this setting is absolutely necessary, check the operation and confirm that there are

no safety problems.

• When two or more signals are allocated to the same output circuit, a signal is output

with OR logic circuit.