Cvp registers – Altera Arria V Avalon-ST User Manual

Page 105

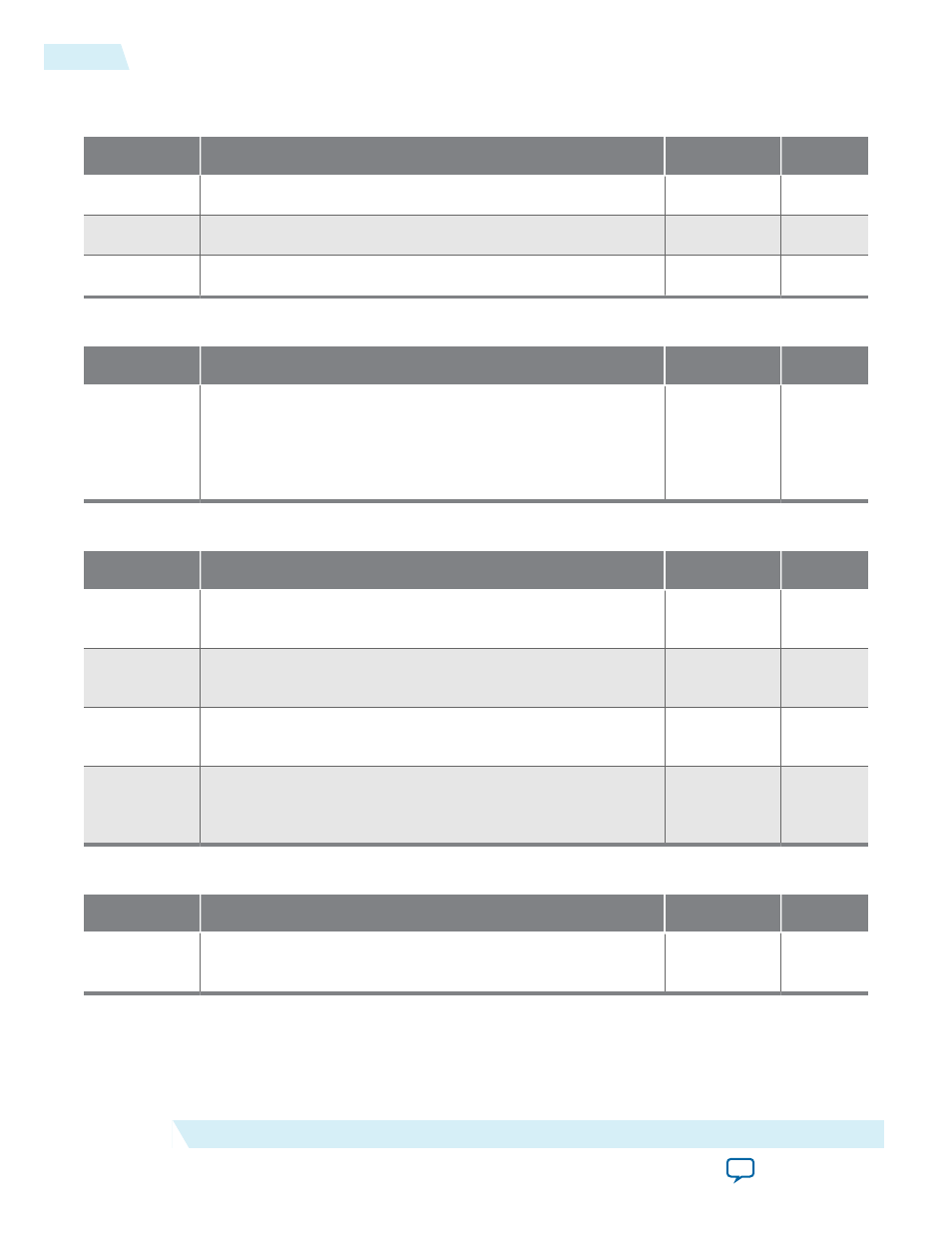

Table 5-3: Altera‑Defined Vendor Specific Header

You can specify these values when you instantiate the Hard IP. These registers are read-only at run-time.

Bits

Register Description

Value

Access

[15:0]

VSEC ID

. A user configurable VSEC ID.

User entered

RO

[19:16]

VSEC Revision

. A user configurable VSEC revision.

Variable

RO

[31:20]

VSEC Length

. Total length of this structure in bytes.

0x044

RO

Table 5-4: Altera Marker Register

Bits

Register Description

Value

Access

[31:0]

Altera Marker

. This read only register is an additional marker. If

you use the standard Altera Programmer software to configure

the device with CvP, this marker provides a value that the

programming software reads to ensure that it is operating with

the correct VSEC.

A Device

Value

RO

Table 5-5: JTAG Silicon ID Register

Bits

Register Description

Value

Access

[127:96]

JTAG Silicon ID DW3

Application

Specific

RO

[95:64]

JTAG Silicon ID DW2

Application

Specific

RO

[63:32]

JTAG Silicon ID DW1

Application

Specific

RO

[31:0]

JTAG Silicon ID DW0

. This is the JTAG Silicon ID that CvP

programming software reads to determine that the correct SRAM

object file (.sof) is being used.

Application

Specific

RO

Table 5-6: User Device or Board Type ID Register

Bits

Register Description

Value

Access

[15:0]

Configurable device or board type ID to specify to CvP the

correct .sof.

Variable

RO

CvP Registers

5-10

CvP Registers

2014.12.15

Altera Corporation

Registers