Altera Arria V Avalon-ST User Manual

Page 230

packets can be transmitted. If you encounter link training issues, viewing the actual data in hardware

should help you determine the root cause. You can use the following tools to provide hardware visibility:

• SignalTap II Embedded Logic Analyzer

• Third-party PCIe analyzer

You can use SignalTap II Embedded Logic Analyzer to diagnose the LTSSM state transitions that are

occurring on the PIPE interface. The

ltssmstate[4:0]

bus encodes the status of LTSSM. The LTSSM

state machine reflects the Physical Layer’s progress through the link training process. For a complete

description of the states these signals encode, refer to Status, Link Training and Reset Signals. When link

training completes successfully and the link is up, the LTSSM should remain stable in the L0 state. When

link issues occur, you can monitor

ltssmstate[4:0]

to determine the cause.

Related Information

Debugging Link Failure in L0 Due To Deassertion of tx_st_ready

There are many reasons that link may stop transmitting data. The following table lists some possible

causes.

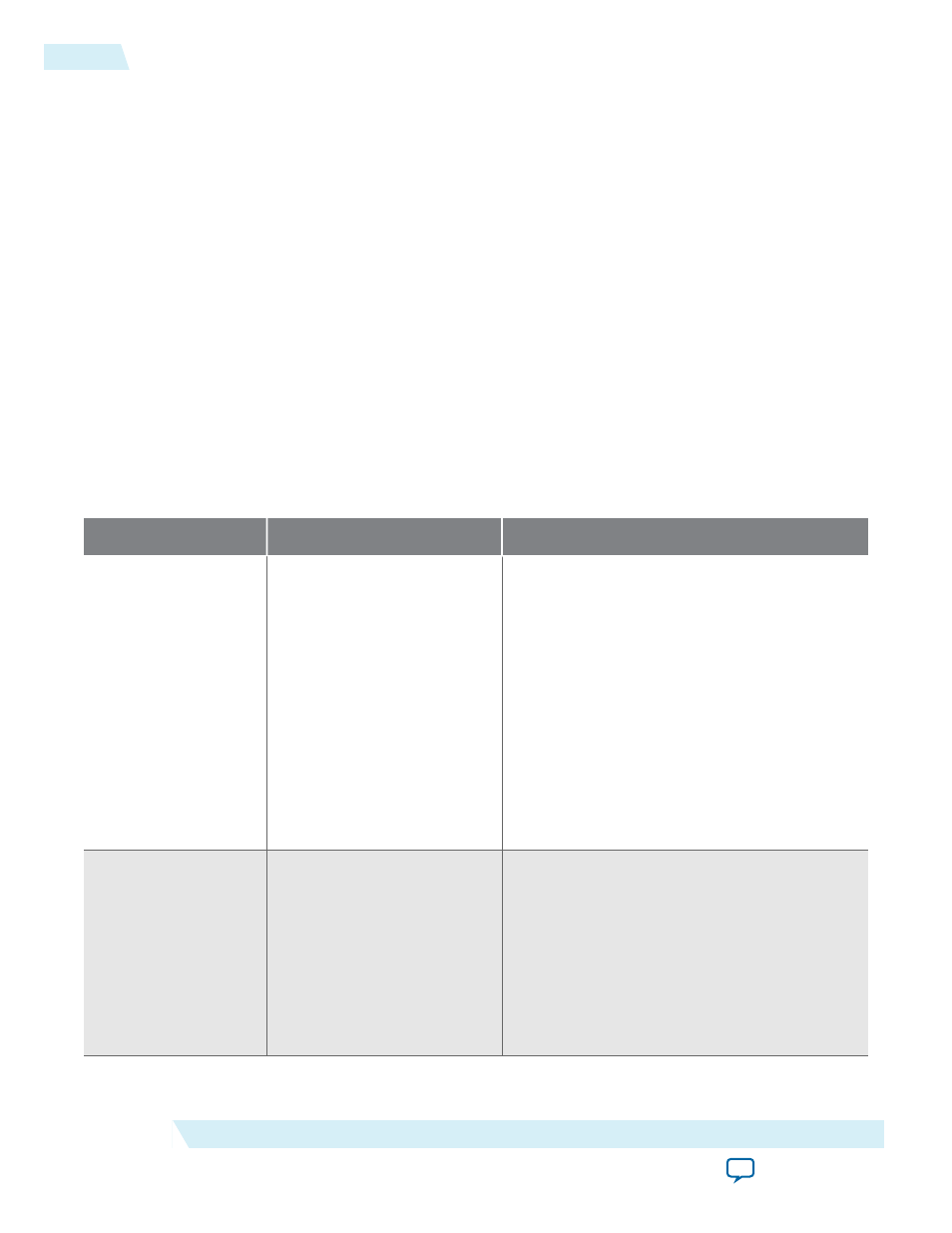

Table 17-1: Link Hangs in L0

Possible Causes

Symptoms and Root Causes

Workarounds and Solutions

Avalon-ST signaling

violates Avalon-ST

protocol

Avalon-ST protocol violations

include the following errors:

• More than one

tx_st_sop

per

tx_st_eop

.

• Two or more

tx_st_eop’s

without a corresponding

tx_

st_sop.

•

rx_st_valid

is not asserted

with

tx_st_sop

or

tx_st_

eop

.

These errors are applicable to

both simulation and hardware.

Add logic to detect situations where

tx_st_

ready

remains deasserted for more than 100

cycles. Set post-triggering conditions to check

for the Avalon-ST signalling of last two TLPs to

verify correct

tx_st_sop

and

tx_st_eop

signalling.

Incorrect payload

size

Determine if the length field of

the last TLP transmitted by End

Point is greater than the InitFC

credit advertised by the link

partner. For simulation, refer to

the log file and simulation

dump. For hardware, use a

third-party logic analyzer trace

to capture PCIe transactions.

If the payload is greater than the initFC credit

advertised, you must either increase the InitFC

of the posted request to be greater than the max

payload size or reduce the payload size of the

requested TLP to be less than the InitFC value.

17-2

Debugging Link Failure in L0 Due To Deassertion of tx_st_ready

2014.12.15

Altera Corporation

Debugging