Altera Arria V Avalon-ST User Manual

Page 93

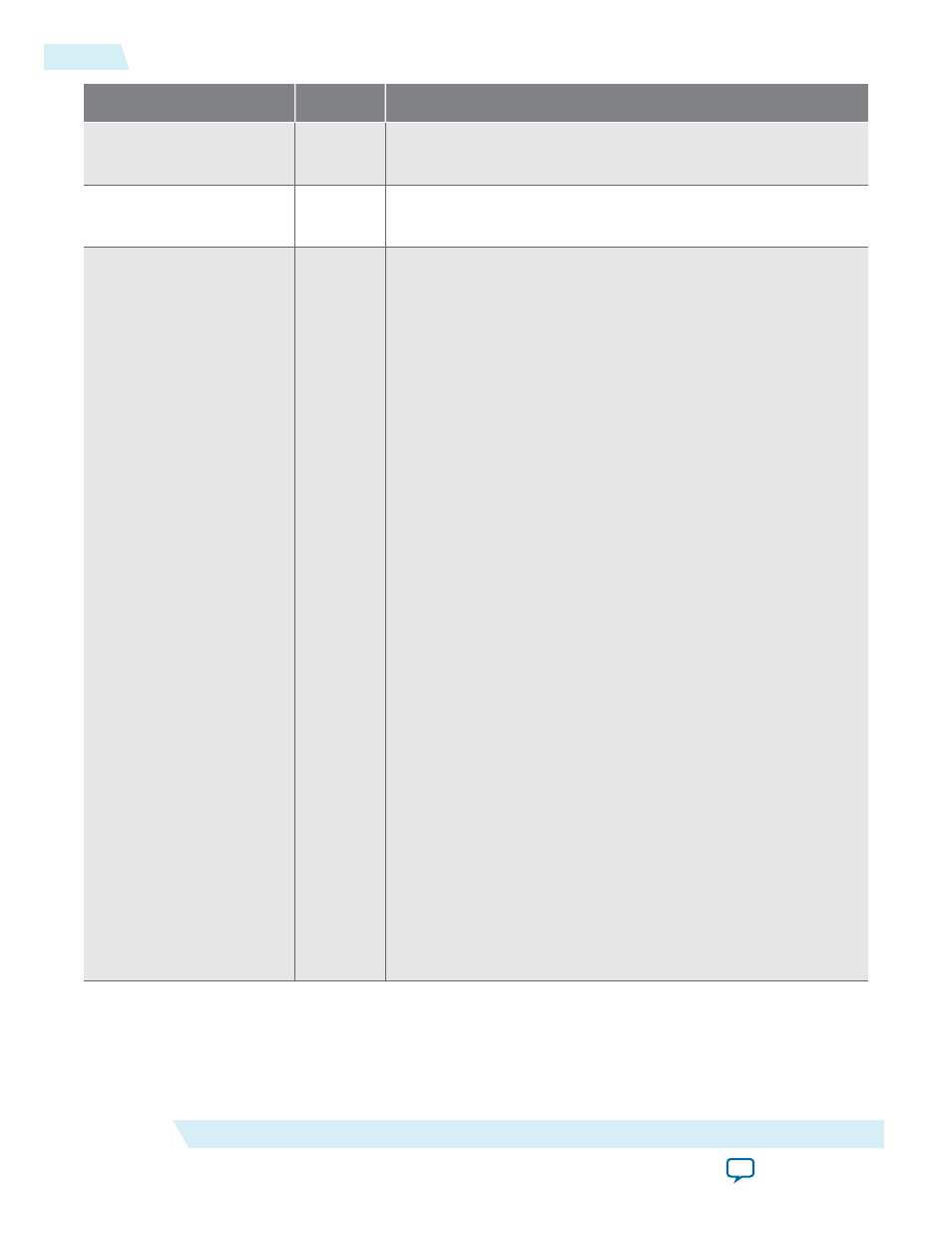

Signal

Direction

Description

rxelecidle0

(1)

Input

Receive electrical idle <n>. When asserted, indicates detection of

an electrical idle.

rxstatus0[2:0]

(1)

Input

Receive status <n>. This signal encodes receive status and error

codes for the receive data stream and receiver detection.

sim_pipe_

ltssmstate0[4:0]

Input and

Output

LTSSM state: The LTSSM state machine encoding defines the

following states:

• 5’b00000: Detect.Quiet

• 5’b 00001: Detect.Active

• 5’b00010: Polling.Active

• 5’b 00011: Polling.Compliance

• 5’b 00100: Polling.Configuration

• 5’b00101: Polling.Speed

• 5’b00110: config.LinkwidthsStart

• 5’b 00111: Config.Linkaccept

• 5’b 01000: Config.Lanenumaccept

• 5’b01001: Config.Lanenumwait

• 5’b01010: Config.Complete

• 5’b 01011: Config.Idle

• 5’b01100: Recovery.Rcvlock

• 5’b01101: Recovery.Rcvconfig

• 5’b01110: Recovery.Idle

• 5’b 01111: L0

• 5’b10000: Disable

• 5’b10001: Loopback.Entry

• 5’b10010: Loopback.Active

• 5’b10011: Loopback.Exit

• 5’b10100: Hot.Reset

• 5’b10101: LOs

• 5’b11001: L2.transmit.Wake

• 5’b11010: Speed.Recovery

• 5’b11011: Recovery.Equalization, Phase 0

• 5’b11100: Recovery.Equalization, Phase 1

• 5’b11101: Recovery.Equalization, Phase 2

• 5’b11110: Recovery.Equalization, Phase 3

• 5’b11111: Recovery.Equalization, Done

4-56

PIPE Interface Signals

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions