Altera Arria V Avalon-ST User Manual

Page 53

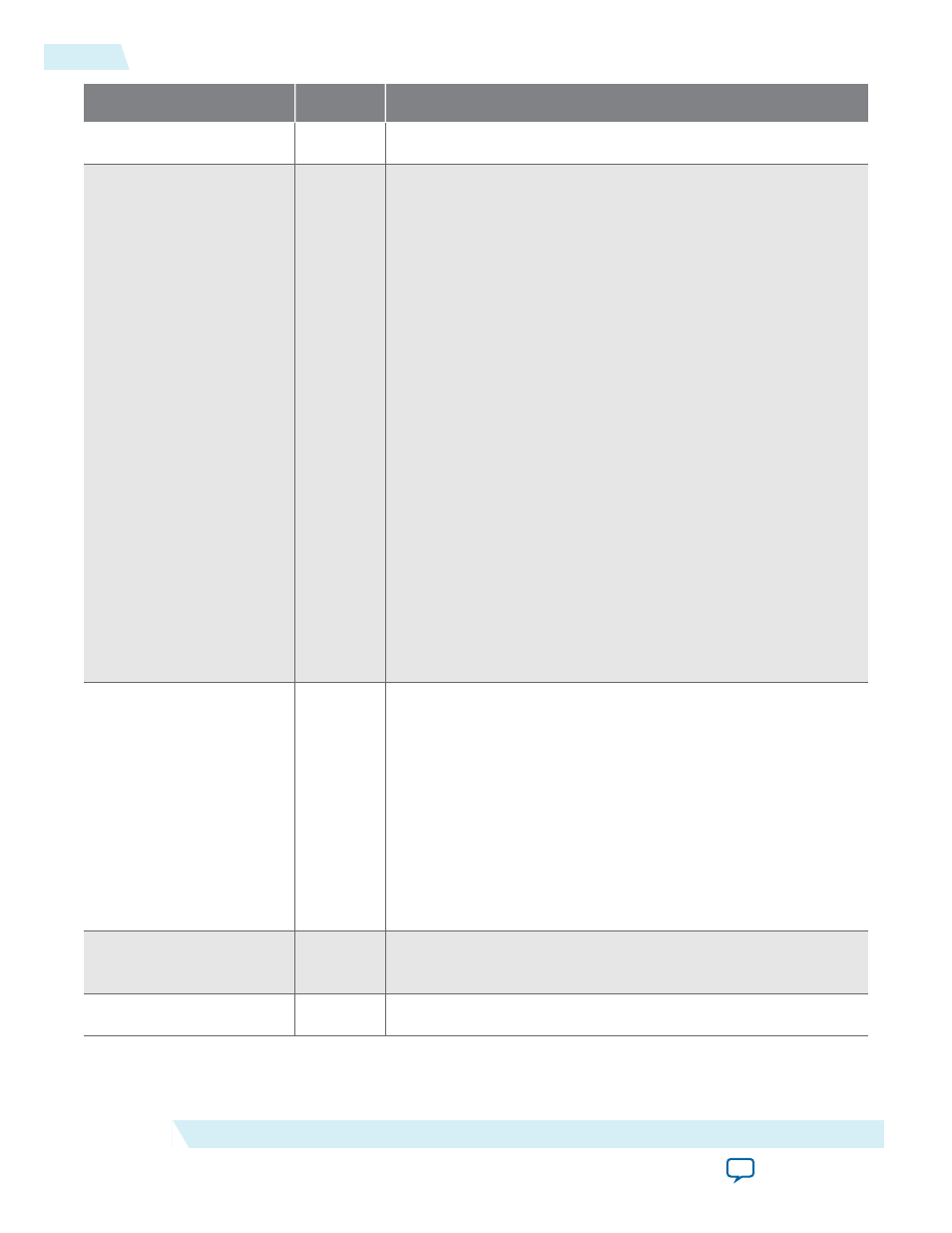

Signal

Direction

Description

tx_cred_datafcp[11:0]

Output

Data credit limit for the FC posted writes. Each credit is 16 bytes.

tx_cred_

fchipcons[5:0]

Output

Asserted for 1 cycle each time the Hard IP consumes a credit.

These credits are from messages that the Hard IP for PCIe

generates for the following reasons:

• To respond to memory read requests

• To send error messages

This signal is not asserted when an Application Layer credit is

consumed. The Application Layer must keep track of its own

consumed credits. To calculate the total credits consumed, the

Application Layer must add its own credits consumed to those

consumed by the Hard IP for PCIe. The credit signals are valid

after

dlup

(data link up) is asserted.

The 6 bits of this vector correspond to the following 6 types of

credit types:

• [5]: posted headers

• [4]: posted data

• [3]: non-posted header

• [2]: non-posted data

• [1]: completion header

• [0]: completion data

During a single cycle, the IP core can consume either a single

header credit or both a header and a data credit.

tx_cred_

fcinfinite[5:0]

Output

When asserted, indicates that the corresponding credit type has

infinite credits available and does not need to calculate credit

limits. The 6 bits of this vector correspond to the following 6

types of credit types:

• [5]: posted headers

• [4]: posted data

• [3]: non-posted header

• [2]: non-posted data

• [1]: completion header

• [0]: completion data

tx_cred_hdrfccp[7:0]

Output

Header credit limit for the FC completions. Each credit is 20

bytes.

tx_cred_hdrfcnp[7:0]

O

Header limit for the non-posted requests. Each credit is 20 bytes.

4-16

Avalon-ST TX Interface

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions