Altera Arria V Avalon-ST User Manual

Page 88

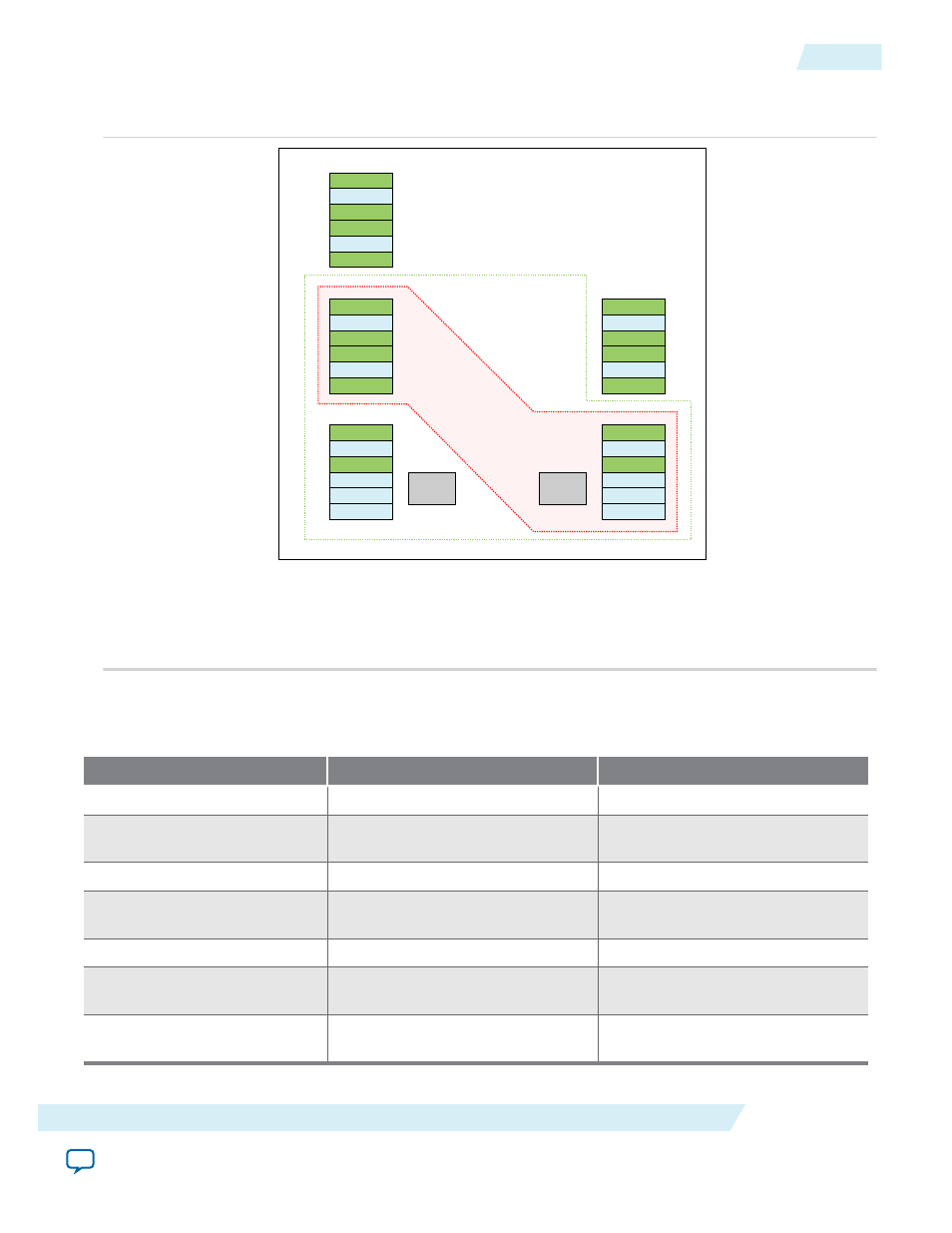

Figure 4-36: Arria V Transceiver Bank and Hard IP for PCI Express IP Core Locations in Arria V SX and ST

Devices

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

Ch5

Ch4

Ch3

Ch2

Ch1

Ch0

12 Ch

18 Ch

30 Ch

GXB_L2

GXB_L1

GXB_L0

GXB_R1

GXB_R0

HIP (1)

HIP

Notes:

1. PCIe HIP availability varies with device variants.

2. Green blocks are 10-Gbps channels.

3. Blue blocks are 6-Gbps channels. With the exception of Ch0 to Ch2 in GXB_L0 and GXB_R0,

the 6-Gbps channels can be used for TX-only or RX-only 10-Gbps channels.

Channel utilization for x1, x2, x4, and x8 variants is as follows:

Table 4-22: Channel Utilization

Variant

Data

CMU Clock

x1, 1 instance

Channel 0 of GXB_L0

Channel 1 of GXB_L0

x1, 2 instances

Channel 0 of GXB_L0, Channel 0 of

GXB_R0

Channel 1 of GXB_L0, Channel 1

of GXB_R0

x2, 1 instance

Channels 1–2 of GXB_L0

Channel 4 of GXB_L0

x2, 2 instances

Channels 1–2 of GXB_L0, Channels

1–2 of GXB_R0

Channel 4 of GXB_L0, Channel 4

of GXB_R0

x4, 1 instance

Channels 0–3 of GXB_L0

Channel 4 of GXB_L0

x4, 2 instances

Channels 0–3 of GXB_L0, Channels

0–3 of GXB_R0

Channel 4 of GXB_L0, Channel 4

of GXB_R0

x8, 1 instance

Channels 0–3 and 5 of GXB_L0 and

channels 0-2 of GXB_L1

Channel 4 of GXB_L0

2014.12.15

Physical Layout of Hard IP in Arria V Devices

4-51

Interfaces and Signal Descriptions

Altera Corporation