Features – Altera Arria V Avalon-ST User Manual

Page 3

Related Information

•

•

•

Features

New features in the Quartus

®

II 14.1 software release:

• Reduced Quartus II compilation warnings by 50%.

The Arria V Hard IP for PCI Express supports the following features:

• Complete protocol stack including the Transaction, Data Link, and Physical Layers implemented as

hard IP.

• Support for ×1, ×2, ×4, and ×8 configurations with Gen1 and Gen2 lane rates for Root Ports and

Endpoints.

• Dedicated 16 KByte receive buffer.

• Optional hard reset controller for Gen2.

• Optional support for Configuration via Protocol (CvP) using the PCIe link allowing the I/O and core

bitstreams to be stored separately.

• Qsys example designs demonstrating parameterization, design modules, and connectivity.

• Extended credit allocation settings to better optimize the RX buffer space based on application type.

• Multi-function support for up to eight Endpoint functions.

• Optional end-to-end cyclic redundancy code (ECRC) generation and checking and advanced error

reporting (AER) for high reliability applications.

Easy to use:

• Flexible configuration.

• Substantial on-chip resource savings and guaranteed timing closure.

• No license requirement.

• Example designs to get started.

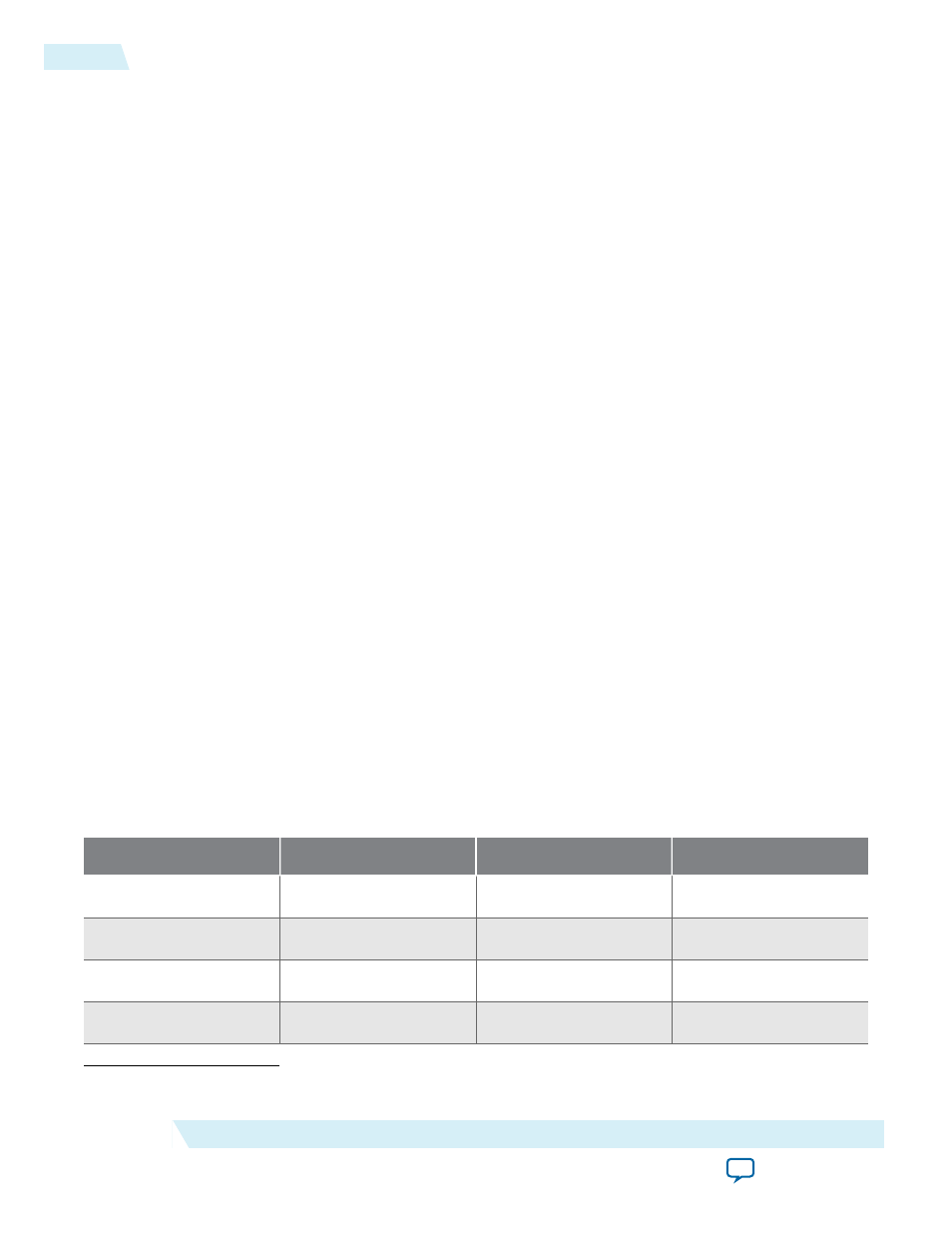

Table 1-2: Feature Comparison for all Hard IP for PCI Express IP Cores

The table compares the features of the four Hard IP for PCI Express IP Cores.

Feature

Avalon‑ST Interface

Avalon‑MM Interface

Avalon‑MM DMA

IP Core License

Free

Free

Free

Native Endpoint

Supported

Supported

Supported

Legacy Endpoint

(1)

Supported

Not Supported

Not Supported

Root port

Supported

Supported

Not Supported

(1)

Not recommended for new designs.

1-2

Features

2014.12.15

Altera Corporation

Datasheet