Altera Arria V Avalon-ST User Manual

Page 73

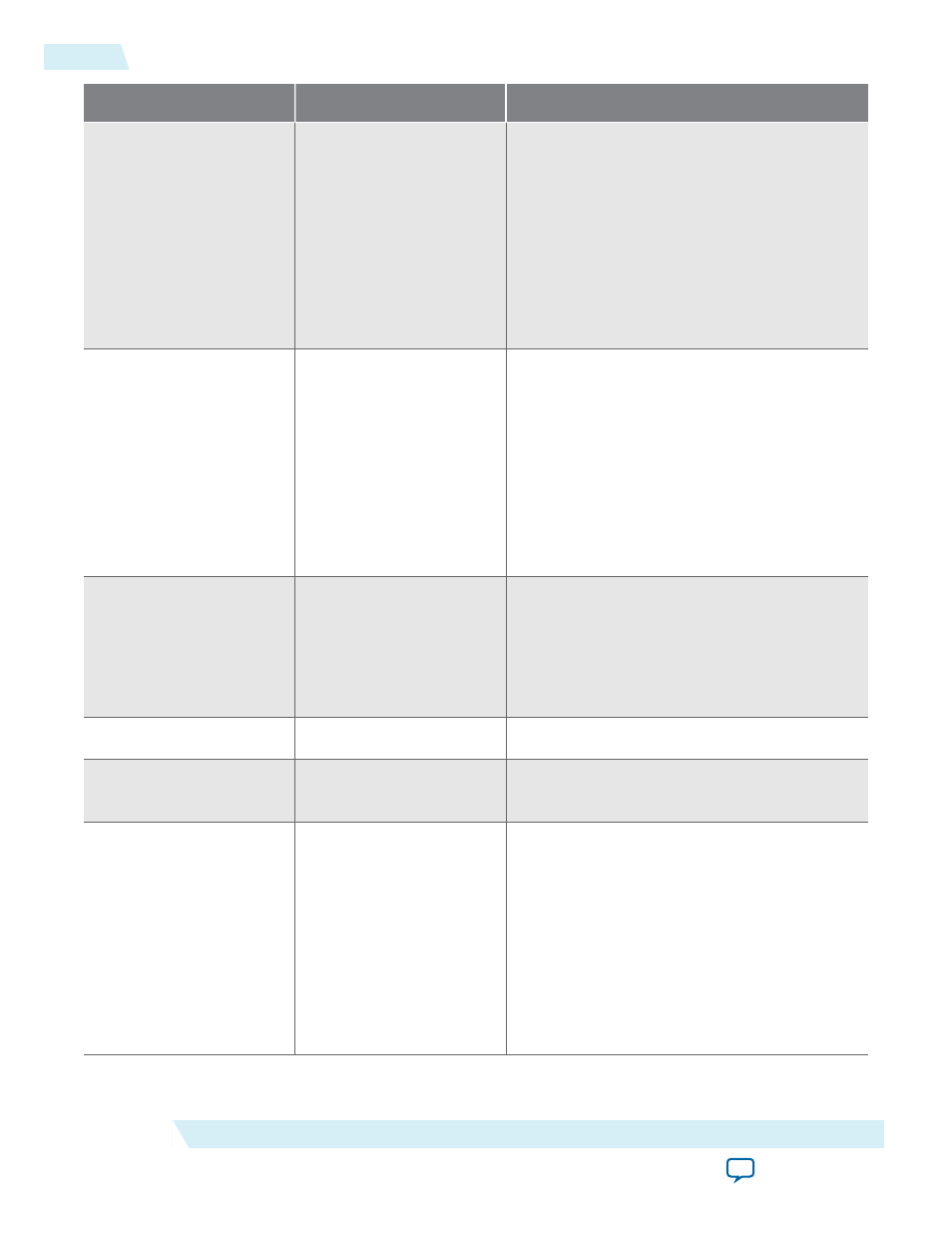

tl_cfg_sts

Configuration Space Register

Description

[58:54] Func1

[68:64] Func2

[78:74] Func3

[88:84] Func4

[98:94] Func5

[108:104] Func6

[118:114] Func7

Link Status Reg[15:11]

Link status bits as follows:

• Bit 15: link autonomous bandwidth status

• Bit 14: link bandwidth management status

• Bit 13: Data Link Layer link active

• Bit 12: slot clock configuration

• Bit 11: link training

[53] Func1

[63] Func2

[73] Func3

[83] Func4

[93] Func5

[103] Func6

[113] Func7

Secondary Status Reg[8]

6th primary command status error bit. Master

data parity error.

[52:49]

Device Status Reg[3:0]

Records the following errors:

• Bit 3: unsupported request detected

• Bit 2: fatal error detected

• Bit 1: non-fatal error detected

• Bit 0: correctable error detected

[48]

Slot Status Register[8]

Data Link Layer state changed

[47]

Slot Status Reg[4]

Command completed. (The hot plug controller

completed a command.)

[46:31]

Link Status Reg[15:0]

Records the following link status information:

• Bit 15: link autonomous bandwidth status

• Bit 14: link bandwidth management status

• Bit 13: Data Link Layer link active

• Bit 12: Slot clock configuration

• Bit 11: Link Training

• Bit 10: Undefined

• Bits[9:4]: Negotiated Link Width

• Bits[3:0] Link Speed

4-36

Transaction Layer Configuration Space Signals

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions