Avalon‑st rx interface – Altera Arria V Avalon-ST User Manual

Page 39

Related Information

•

•

on page 2-2

Arria V Hard IP for PCI Express with Avalon-ST Interface to the

Application Layer

Avalon‑ST RX Interface

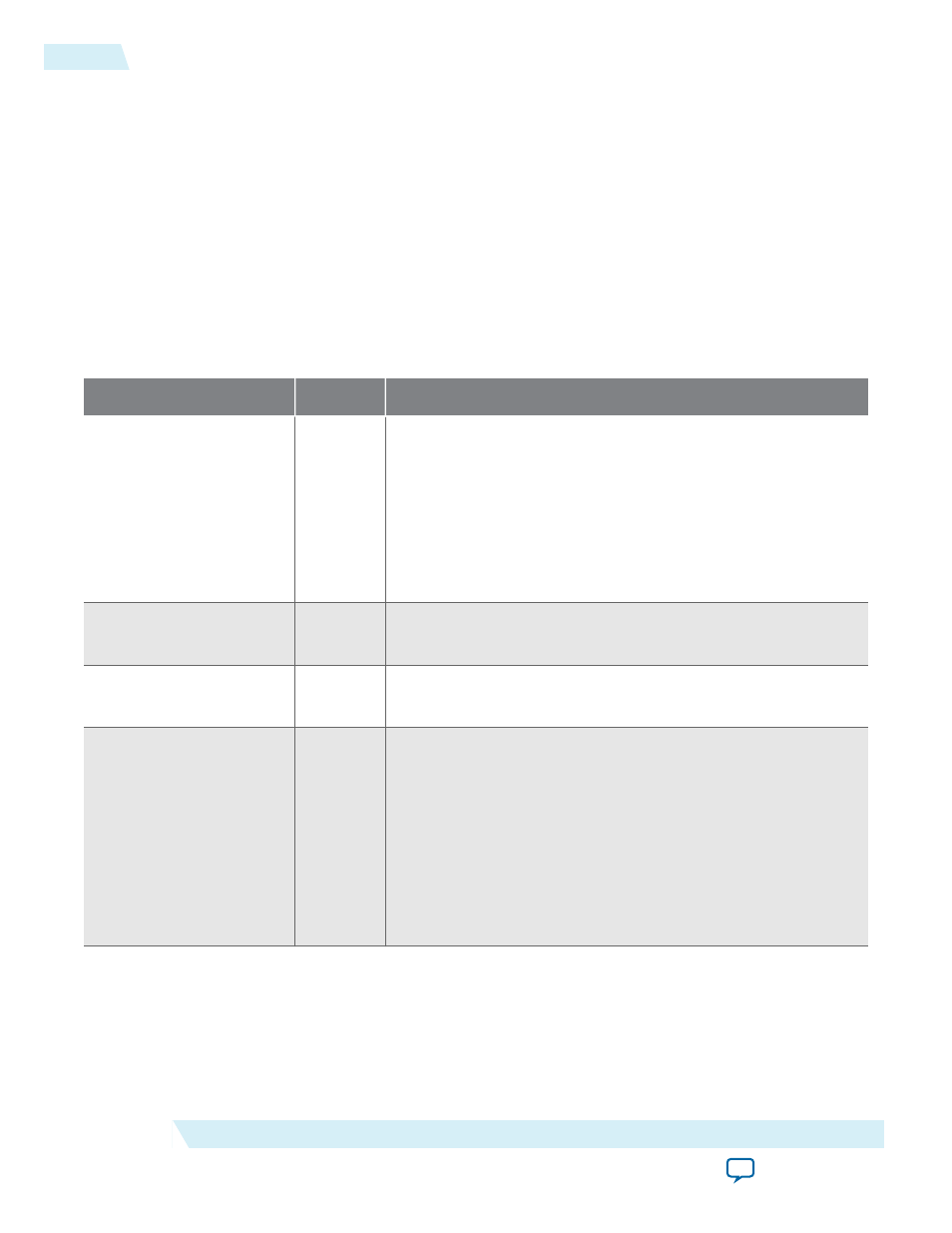

Table 4-1: 64- or 128‑Bit Avalon-ST RX Datapath

The RX data signal can be 64 or 128 bits.

Signal

Direction

Description

rx_st_data[<n>-1:0]

Output

Receive data bus. Refer to figures following this table for the

mapping of the Transaction Layer’s TLP information to

rx_st_

data

and examples of the timing of this interface. Note that the

position of the first payload dword depends on whether the TLP

address is qword aligned. The mapping of message TLPs is the

same as the mapping of TLPs with 4-dword headers. When using

a 64-bit Avalon-ST bus, the width of

rx_st_data

is 64. When

using a 128-bit Avalon-ST bus, the width of

rx_st_data

is 128.

rx_st_sop

Output

Indicates that this is the first cycle of the TLP when

rx_st_valid

is asserted.

rx_st_eop

Output

Indicates that this is the last cycle of the TLP when

rx_st_valid

is asserted.

rx_st_empty

Output

Indicates the number of empty qwords in

rx_st_data

. Not used

when

rx_st_data

is 64 bits. Valid only when

rx_st_eop

is

asserted in 128-bit mode.

For 128-bit data, only bit 0 applies; this bit indicates whether the

upper qword contains data.

• 128-Bit interface:

•

rx_st_empty

= 0,

rx_st_data[127:0]

contains valid data

•

rx_st_empty = 1

,

rx_st_data[63:0]

contains valid data

4-2

Arria V Hard IP for PCI Express with Avalon-ST Interface to the Application Layer

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions