Transceiver phy ip reconfiguration – Altera Arria V Avalon-ST User Manual

Page 168

Transceiver PHY IP Reconfiguration

15

2014.12.15

As silicon progresses towards smaller process nodes, circuit performance is affected by variations due to

process, voltage, and temperature (PVT). Designs typically require offset cancellation to ensure correct

operation. At Gen2 data rates, designs also require DCD calibration. Altera’s Qsys example designs all

include Transceiver Reconfiguration Controller and Altera PCIe Reconfig Driver IP cores to perform

these functions.

Connecting the Transceiver Reconfiguration Controller IP Core

The Transceiver Reconfiguration Controller IP Core is available for V-series devices and can be found in

the Interface Protocols/Transceiver PHY category in the IP Catalog. When you instantiate the

Transceiver Reconfiguration Controller the Enable offset cancellation block and Enable PLL calibration

options are enabled by default.

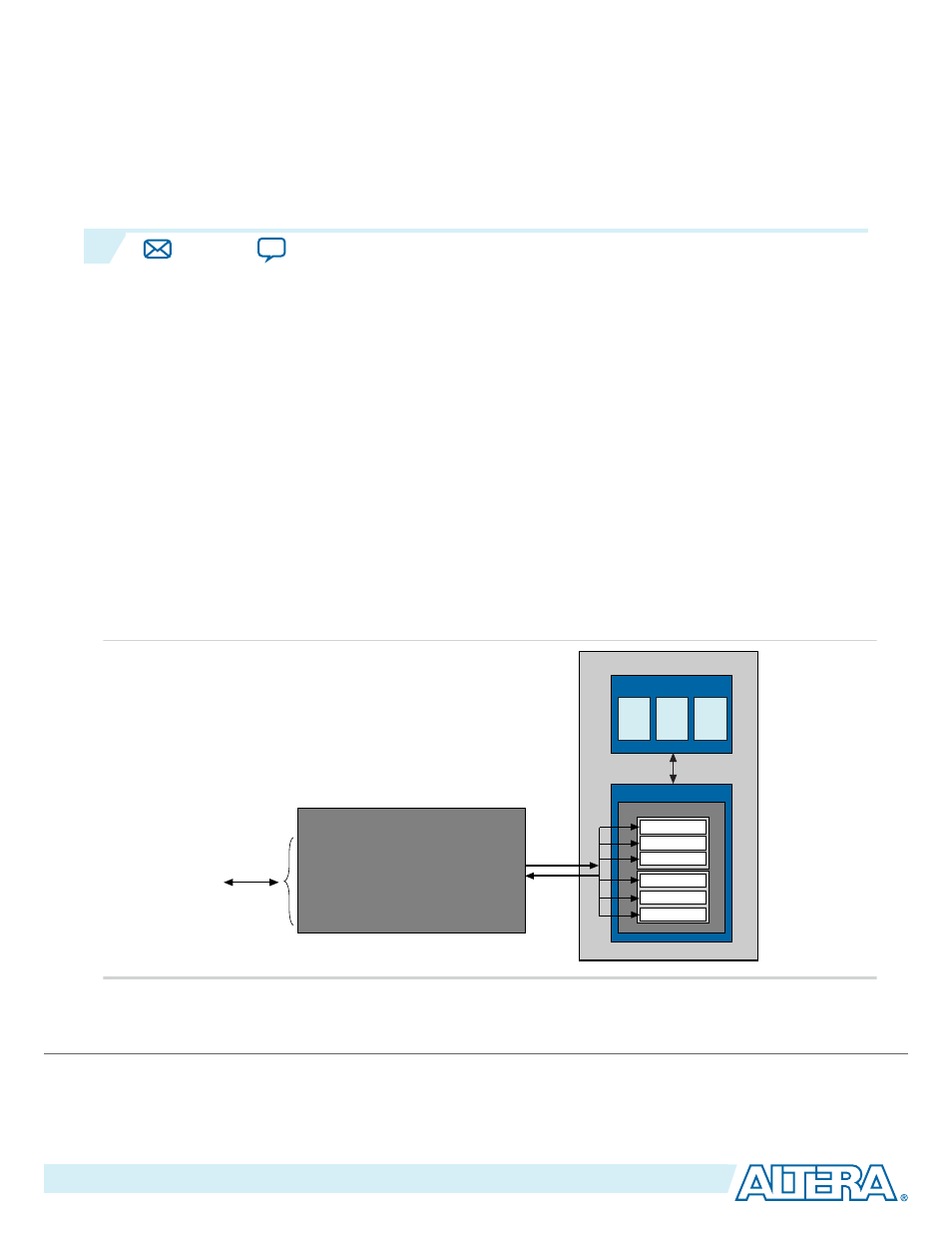

Figure 15-1: Altera Transceiver Reconfiguration Controller Connectivity

The following figure shows the connections between the Transceiver Reconfiguration Controller instance

and the PHY IP Core for PCI Express instance for a ×4 variant.

Avalon-MM

Slave Interface

PHY IP Core for PCI Express

Lane 2

Lane 3

Lane 1

Lane 0

TX PLL

Transceiver Bank

to and from

Embedded

Controller

100-125 MHz

Transceiver Reconfiguration Controller

(Unused)

mgmt_clk_clk

mgmt_rst_reset

reconfig_mgmt_address[6:0]

reconfig_mgmt_writedata[31:0]

reconfig_mgmt_readdata[31:0]

reconfig_mgmt_write

reconfig_mgmt_read

reconfig_mgmt_waitrequest

reconfig_to_xcvr

reconfig_from_xcvr

Hard IP for PCI Express Variant

Hard IP for PCI Express

Trans-

action

Data

Link

PHY

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134