Altera Arria V Avalon-ST User Manual

Page 98

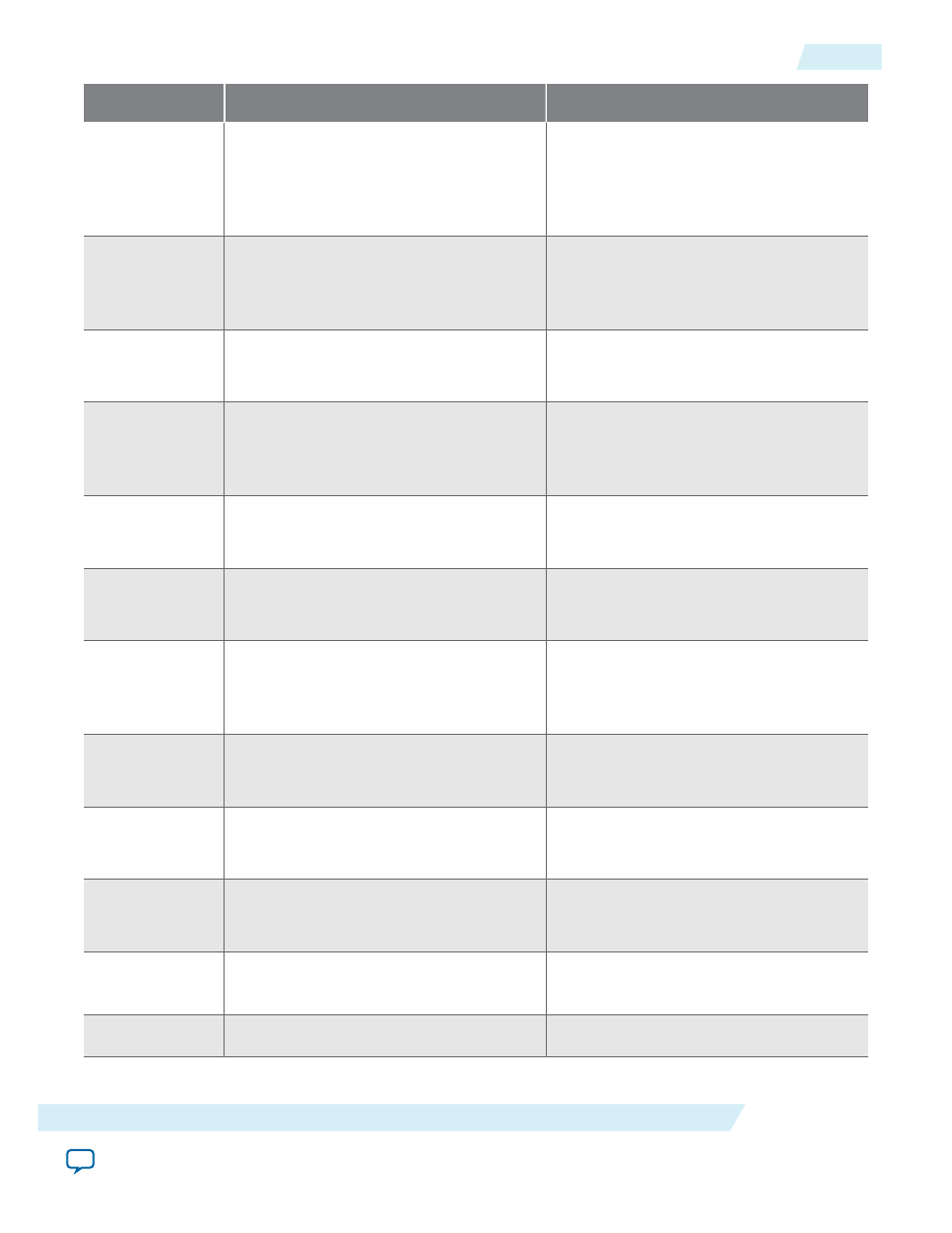

Byte Address

Hard IP Configuration Space Register

Corresponding Section in PCIe Specification

0x018

Base Address 2

Secondary Latency Timer, Subordinate Bus

Number, Secondary Bus Number, Primary

Bus Number

Base Address Registers

Secondary Latency Timer, Type 1

Configuration Space Header, Primary

Bus Number

0x01C

Base Address 3

Secondary Status, I/O Limit, I/O Base

Base Address Registers

Secondary Status Register ,Type 1

Configuration Space Header

0x020

Base Address 4

Memory Limit, Memory Base

Base Address Registers

Type 1 Configuration Space Header

0x024

Base Address 5

Prefetchable Memory Limit, Prefetchable

Memory Base

Base Address Registers

Prefetchable Memory Limit, Prefetchable

Memory Base

0x028

Reserved

Prefetchable Base Upper 32 Bits

N/A

Type 1 Configuration Space Header

0x02C

Subsystem ID, Subsystem Vendor ID

Prefetchable Limit Upper 32 Bits

Type 0 Configuration Space Header

Type 1 Configuration Space Header

0x030

Expansion ROM base address

I/O Limit Upper 16 Bits, I/O Base Upper 16

Bits

Type 0 Configuration Space Header

Type 1 Configuration Space Header

0x034

Reserved, Capabilities PTR

Type 0 Configuration Space Header

Type 1 Configuration Space Header

0x038

Reserved

Expansion ROM Base Address

N/A

Type 1 Configuration Space Header

0x03C

Interrupt Pin, Interrupt Line

Bridge Control, Interrupt Pin, Interrupt Line

Type 0 Configuration Space Header

Type 1 Configuration Space Header

0x050

MSI-Message Control Next Cap Ptr

Capability ID

MSI and MSI-X Capability Structures

0x054

Message Address

MSI and MSI-X Capability Structures

2014.12.15

Correspondence between Configuration Space Registers and the PCIe Specification

5-3

Registers

Altera Corporation