Physical layer interface signals – Altera Arria V Avalon-ST User Manual

Page 84

Bits

Field

Description

[15]

PME_status

When set to 1, indicates that the function would normally assert

the

PME#

message independently of the state of the

PME_en

bit.

[14:13]

data_scale

This field indicates the scaling factor when interpreting the value

retrieved from the data register. This field is read-only.

[12:9]

data_select

This field indicates which data should be reported through the

data register and the

data_scale

field.

[8]

PME_EN

1: indicates that the function can assert PME#0: indicates that the

function cannot assert PME#

[7:2]

reserved

—

[1:0]

PM_state

Specifies the power management state of the operating condition

being described. The following encodings are defined:

• 2b’00 D0

• 2b’01 D1

• 2b’10 D2

• 2b’11 D3

A device returns 2b’11 in this field and

Aux

or

PME Aux

in the

type

register to specify the D3-Cold PM state. An encoding of

2b’11 along with any other

type

register value specifies the D3-

Hot state.

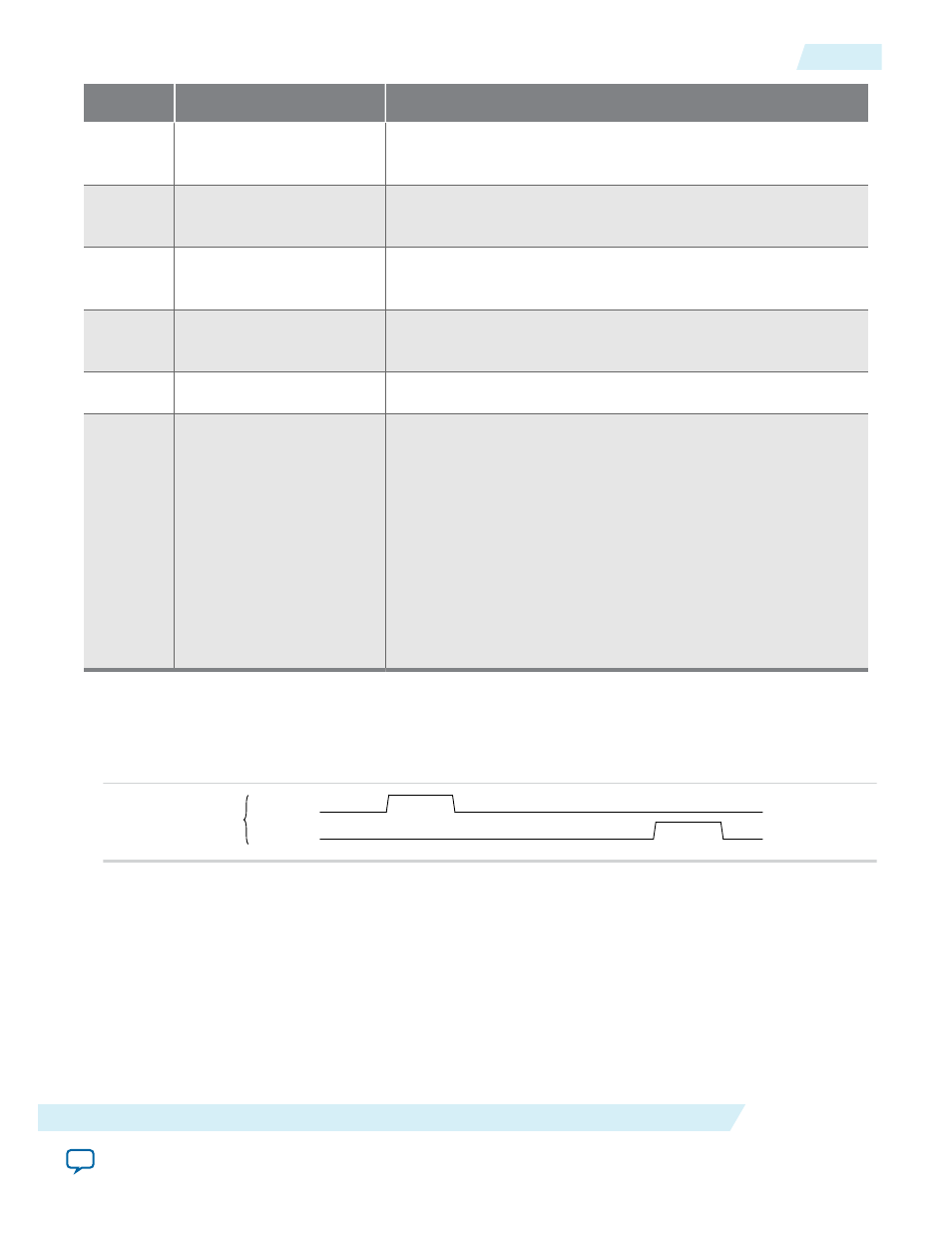

Figure 4-34: pme_to_sr and pme_to_cr in an Endpoint IP core

The following figure illustrates the behavior of

pme_to_sr

and

pme_to_cr

in an Endpoint. First, the Hard

IP receives the

PME_turn_off

message which causes

pme_to_sr

to assert. Then, the Application Layer

sends the

PME_to_ack

message to the Root Port by asserting

pme_to_cr

.

pme_to_sr

pme_to_cr

hard

IP

Physical Layer Interface Signals

Altera provides an integrated solution with the Transaction, Data Link and Physical Layers. The IP

Parameter Editor generates a SERDES variation file,

<variation>_serdes.v

or .vhd , in addition to the Hard

IP variation file,

<variation>.v

or

.vhd

. The SERDES entity is included in the library files for PCI Express.

2014.12.15

Physical Layer Interface Signals

4-47

Interfaces and Signal Descriptions

Altera Corporation