Altera Arria V Avalon-ST User Manual

Page 45

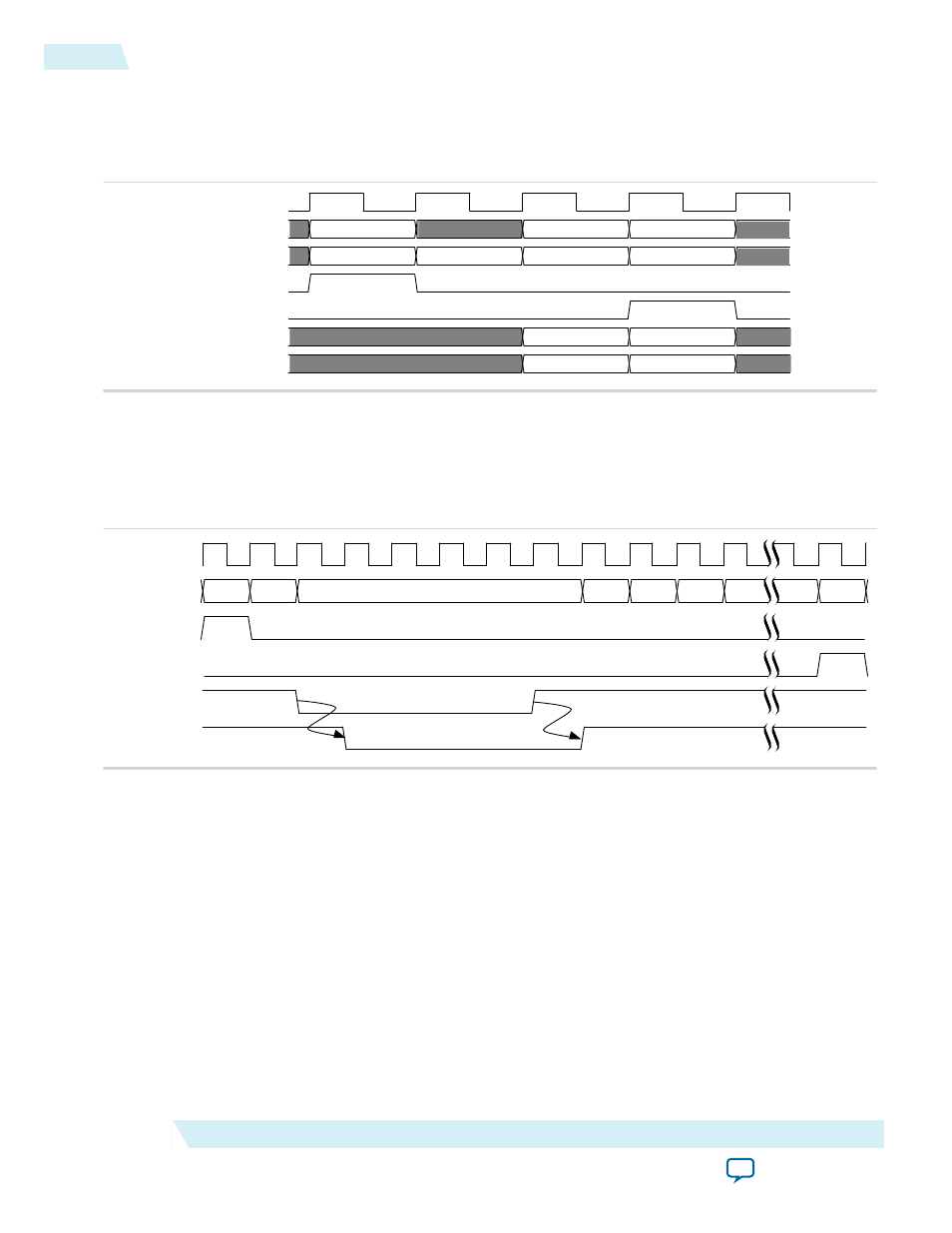

Figure 4-4: 64-Bit Avalon-ST rx_st_data<n> Cycle Definition for 3-Dword Header TLPs with Qword

Aligned Address

In the following figure,

rx_st_be[7:4]

corresponds to

rx_st_data[63:32]

.

rx_st_be[3:0]

corresponds to

rx_st_data[31:0]

.

clk

rx_st_data[63:32]

rx_st_data[31:0]

rx_st_sop

rx_st_eop

rx_st_be[7:4]

rx_st_be[3:0]

Header 1

Data1

Data3

Header 0

Header2

Data0

Data2

F

1

F

E

Figure 4-5: 64-Bit Application Layer Backpressures Transaction Layer

The following figure illustrates the timing of the RX interface when the Application Layer backpressures

the Arria V Hard IP for PCI Express by deasserting

rx

_st_ready

. The

rx_st_valid

signal deasserts

within three cycles after

rx_st_ready

is deasserted. In this example,

rx_st_valid

is deasserted in the

next cycle.

rx_st_data

is held until the Application Layer is able to accept it.

pld_clk

rx_st_data[63:0]

rx_st_sop

rx_st_eop

rx_st_ready

rx_st_valid

000 . 010 .

CCCC0002CCCC0001

CC

. CC

. CC

. CC

. CC

. CC

.

4-8

Data Alignment and Timing for the 64‑Bit Avalon‑ST RX Interface

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions