Summary of pll output clocks – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 11

Select Use these clock settings for the DPA clock if you want the output clock signal of the PLL to drive

the input clock port of the DPA block in the ALTLVDS IP core. This option is available only for Stratix III

and Stratix IV devices.

Parameter Settings When “Set up PLL in LVDS mode” Option is Enabled

The following parameter settings apply only when Set up PLL in LVDS Mode is turned on for Arria GX,

Stratix II, Stratix II GX, and HardCopy II fast PLLs.

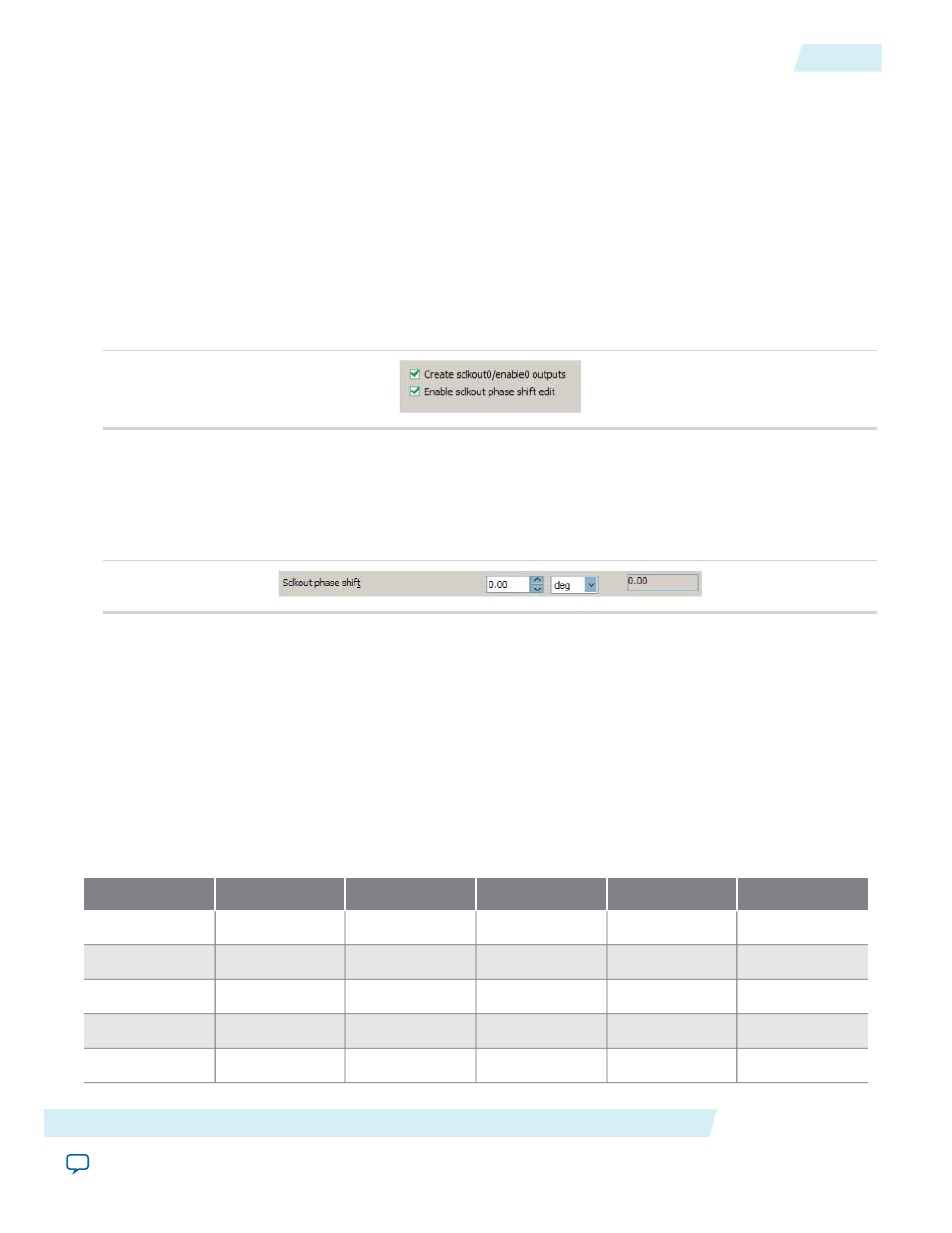

When you turn on Set up PLL in LVDS mode, two additional options are available on the Output Clocks

pages for c0 and c1.

The following figure shows the additional options to configure the

c0

output clock signal.

Figure 6: Additional Options to Configure the c0 Output Clock Signal

Turn on Create sclkout0/enable0 outputs to create the

sclkout0

and

enable0

ports. The

sclkout0

port

is the serial clock output port, and the

enable0

port is the enable port.

The following figure shows the additional options to configure the

c0

output clock signal.

Figure 7: Sclkout Phase Shift Option

The

sclkout

phase shift option allows you to edit the phase shift of the

sclkout

signal (in this case, the

sclkout0

signal).

Only two pairs of

sclkout

and

enable

ports can be created in an ALTPLL IP core. The

sclkout0

and

enable0

ports are for the

c0

output clock, and the

sclkout1

and

enable1

ports are for the

c1

output clock.

Summary of PLL Output Clocks

The following table summarizes and compares properties of the clock output ports per PLL for each PLL

type in the supported device families. The number of clock output ports shown in the table for each device

family can be set as internal or external clock output port unless described otherwise.

Table 6: Number of Clock Output Ports per PLL

Cyclone Series PLL

Fast PLL

Enhanced PLL

Left_Right

Top_Bottom

Device Family

—

4

6

—

—

Arria GX

—

—

—

7

—

Arria II GX

—

—

—

7

10

Stratix IV

—

—

—

7

10

Stratix III

—

4

6

—

—

Stratix II

Altera Corporation

ALTPLL (Phase-Locked Loop) IP Core User Guide

11

Parameter Settings When “Set up PLL in LVDS mode” Option is Enabled

ug-altpll

2014.08.18