Altpll bidirectional port, Altpll parameters – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 46

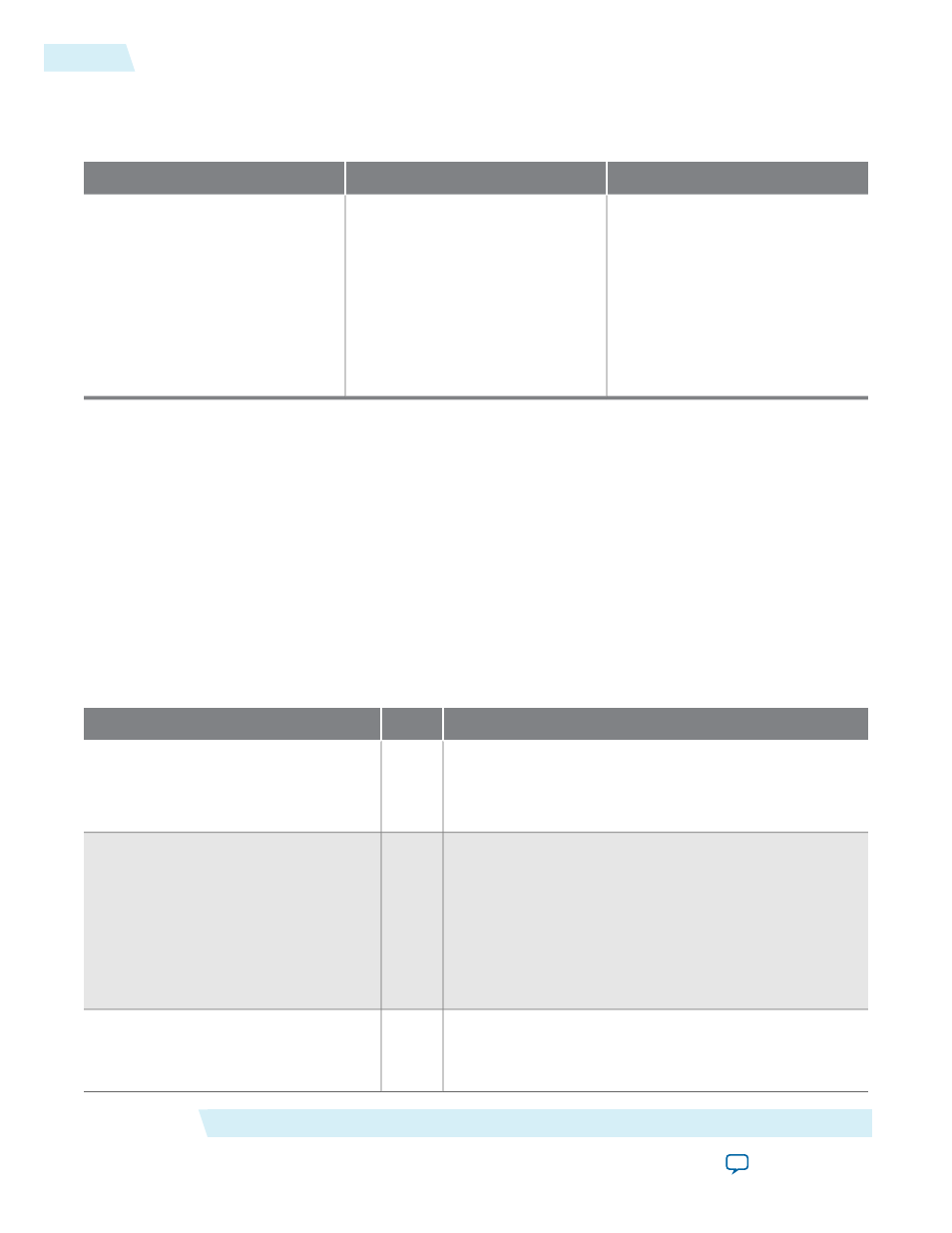

ALTPLL Bidirectional Port

Table 18: ALTPLL Bidirectional Output Port

Description

Condition

Port Name

The bidirectional port that

connects to the mimic circuitry.

This port is available only for

Stratix III and Stratix IV device

families, and only when the PLL

is in zero-delay buffer mode. This

port must be connected to a

bidirectional pin that is placed on

the positive feedback dedicated

output pin of the PLL.

Optional

fbmimicbidir

ALTPLL Parameters

In the ALTPLL parameters, the

c[]

and

e[]

ports are named

CLK[]

and

EXTCLK[]

, respectively. This is to

differentiate them from the parameters used to describe the C and E counters of the PLL.

Replace the brackets,

[]

, in the parameter name with an integer to get the exact parameter name. For example,

the

C[]_HIGH

parameter can have up to 10 variations as described in the parameter description. The variations

are

C0_HIGH

,

C1_HIGH

,

C2_HIGH

,

C3_HIGH

,

C4_HIGH

,

C5_HIGH

,

C6_HIGH

,

C7_HIGH

,

C8_HIGH

, and

C9_HIGH

.

A string must be contained within a pair or double quotes. For example, to specify a medium bandwidth

type of PLL,

BANDWIDTH_TYPE

=”MEDIUM”.

An integer must not be contained within a pair or double quotes. For example, to specify a 40% duty cycle

for the output clock port,

c5

,

CLK5_DUTY_CYCLE

=40.

Table 19: ALTPLL Parameters

Description

Type

Parameter

Specifies the bandwidth value of the PLL in MHz. If this

parameter is not specified, the Compiler automatically

determines the value of the

BANDWIDTH

parameter to satisfy

other PLL settings.

String

BANDWIDTH

Specifies the type of bandwidth for the

BANDWIDTH

parameter. Values are

AUTO

,

LOW

,

MEDIUM

, or

HIGH

. If

omitted, the default value is

AUTO

.

For the low bandwidth option, the PLL has a better jitter

rejection but slower lock time. For the high bandwidth

option, the PLL has a faster lock time but tracks more jitter.

The medium option is a balance between the other two

options.

String

BANDWIDTH_TYPE

Specifies the value of the high period count for the

corresponding counter,

C[9..0]

. If omitted, default is

1

.

Counters

C[9..5]

are not available in Cyclone III devices

onwards.

Integer

C[]_HIGH

ALTPLL (Phase-Locked Loop) IP Core User Guide

Altera Corporation

ug-altpll

ALTPLL Bidirectional Port

46

2014.08.18