Ports and parameters, Altpll input ports – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 38

Ports and Parameters

The ALTPLL IP core ports and parameters are available to customize the ALTPLL IP core according to your

application.

The options you select in the parameter editor affect the ports and parameters settings of the IP core. Most

of these options are device-dependent, and some options depend on one another. The options you select

enable the PLL features, and some might generate top-level ports in the ALTPLL IP core.

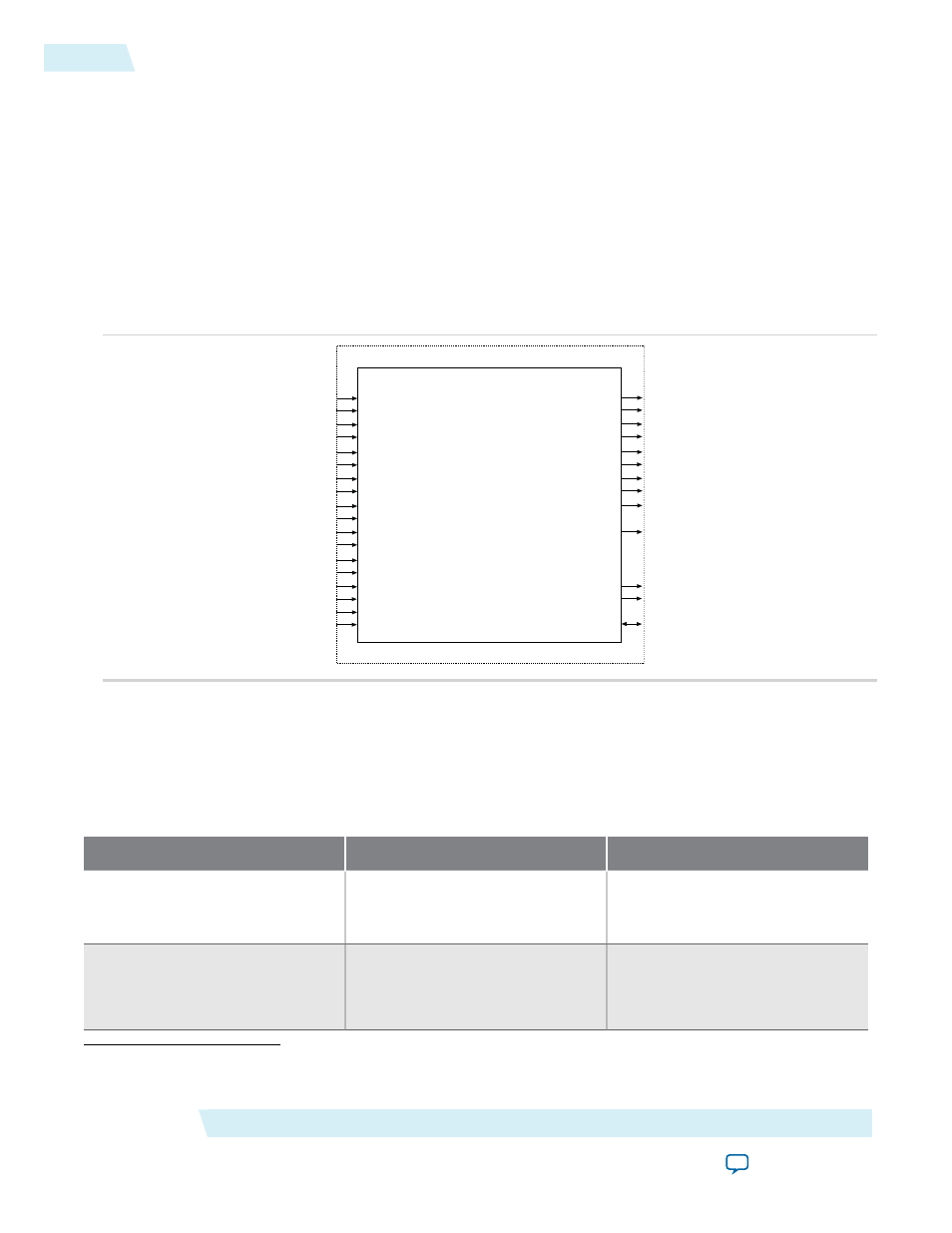

The following figure shows the top-level ports of the ALTPLL IP core.

Figure 27: Input and Output Ports

ALTPLL

inclk[]

fbin

phaseupdown

phasestep

phasecounterselect[]

pllena

clkswitch

areset

pfdena

c[]_ena

e[]_ena

configupdate

scanclk

scanclkena

scanaclr

scandata

scanread

scanwrite

c[]

e[]

clkbad[]

activeclock

clkloss

locked

scandataout

fbout

enable[]

sclkout[]

phasedone

scandone

fbmimicbidir

The parameters are only relevant if you bypass the parameter editor GUI and instantiate the IP core directly

in your design. The details of these parameters are hidden from the parameter editor.

ALTPLL Input Ports

Table 16: ALTPLL Input Ports

Description

Condition

Port Name

(6)

Resets all counters to initial values,

including the

GATE_LOCK_COUNTER

parameter.

Optional

areset

An enable input port for the

output clock,

c[]

. Available for

Stratix and Stratix GX devices

only.

Optional

c[]_ena

(6)

Replace brackets, [], in the port name with integer to get the exact name. For example,

inclk0

,

inclk1

,

c1_

ena

, and

e0_ena

.

ALTPLL (Phase-Locked Loop) IP Core User Guide

Altera Corporation

ug-altpll

Ports and Parameters

38

2014.08.18