Operation modes supported in each device family, Parameter settings – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 4

The following list describes the operation modes for the ALTPLL IP core:

• Normal mode—The PLL feedback path source is a global or regional clock network, minimizing clock

delay to registers for that clock type and specific PLL output. You can specify PLL output that is

compensated in normal mode.

• Source-Synchronous mode—The data and clock signals arrive at the same time at the data and clock

input pins. In this mode, the signals are guaranteed to have the same phase relationship at the clock and

data ports of any Input Output Enable register.

• Zero-Delay Buffer mode—The PLL feedback path is confined to the dedicated PLL external clock output

pin. The clock port driven off-chip is phase aligned with the clock input for a minimal delay between the

clock input and the external clock output.

• No Compensation mode—The PLL feedback path is confined to the PLL loop. It has no clock network

or other external source. A PLL in no-compensation mode has no clock network compensation, but clock

jitter is minimized.

• External Feedback mode—The PLL compensates for the

fbin

feedback input to the PLL. The delay

between the input clock pin and the feedback clock pin is minimized.

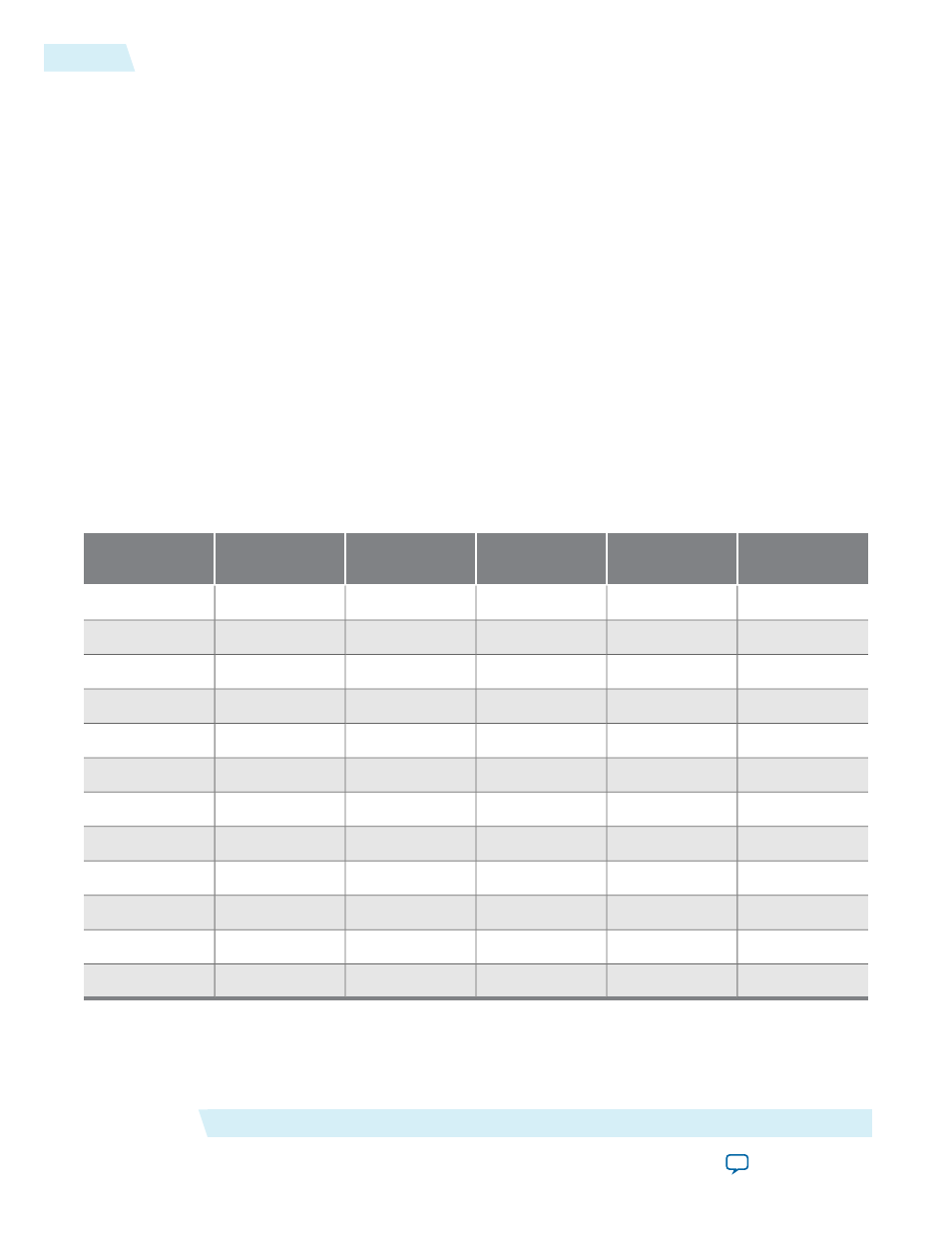

Operation Modes Supported in Each Device Family

The following table summarizes the operation modes supported for each device family.

Table 2: PLL Types and Modes Supported in Different Device Families

External Feedback

No Compensation

Zero-Delay Buffer

Source-

Synchronous

Normal

Device Family

Enhanced PLL

All PLL types

Enhanced PLL

All PLL types

All PLL types

Arria GX

—

Left_Right PLL

Left_Right PLL

Left_Right PLL

Left_Right PLL

Arria II GX

All PLL types

All PLL types

All PLL types

All PLL types

All PLL types

Stratix IV

Enhanced PLL

All PLL types

Enhanced PLL

All PLL types

All PLL types

Stratix III

Enhanced PLL

All PLL types

Enhanced PLL

All PLL types

All PLL types

Stratix II

Enhanced PLL

All PLL types

Enhanced PLL

All PLL types

All PLL types

Stratix II GX

Enhanced PLL

All PLL types

Enhanced PLL

—

All PLL types

Stratix

Enhanced PLL

All PLL types

Enhanced PLL

—

All PLL types

Stratix GX

—

All PLL types

All PLL types

All PLL types

All PLL types

Cyclone IV

—

All PLL types

All PLL types

All PLL types

All PLL types

Cyclone III

—

All PLL types

All PLL types

All PLL types

All PLL types

Cyclone II

—

All PLL types

All PLL types

—

All PLL types

Cyclone

Parameter Settings

Describes how to set the operation mode for the PLL using the ALTPLL parameter editor. The parameter

settings are located on the General/Modes page of the ALTPLL parameter editor.

ALTPLL (Phase-Locked Loop) IP Core User Guide

Altera Corporation

ug-altpll

Operation Modes Supported in Each Device Family

4

2014.08.18