Advanced features, Advanced control signals (pllena, areset, pfdena), Pllena – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 12: Areset

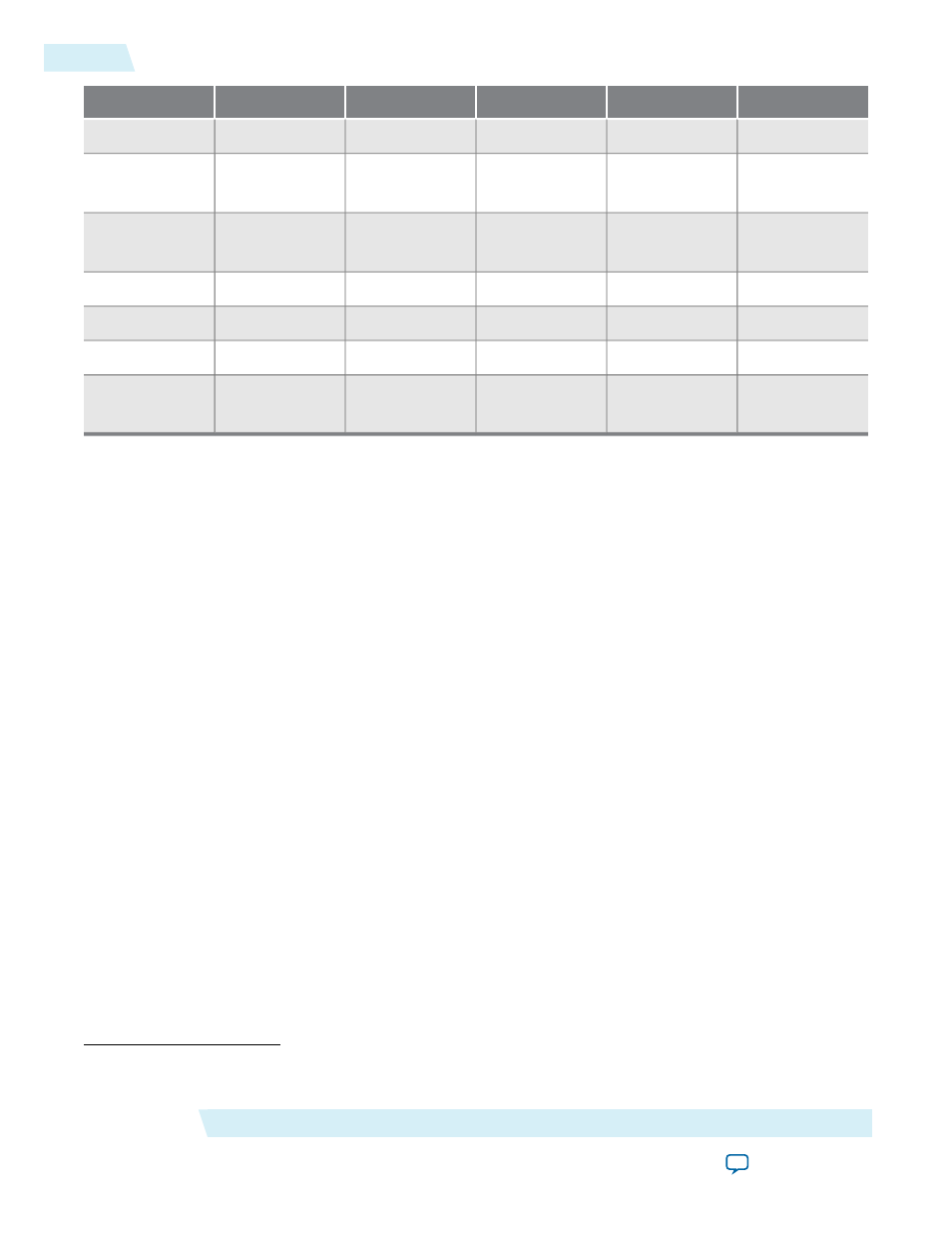

Cyclone Series PLL

Fast PLL

Enhanced PLL

Left_Right

Top_Bottom

Device Family

—

4

6

—

—

Stratix II GX

—

3

6

(1)

—

—

Stratix

—

3

6

(1)

—

—

Stratix GX

5

—

—

—

—

Cyclone IV

5

—

—

—

—

Cyclone III

3

—

—

—

—

Cyclone II

2

(2)

—

—

—

—

Cyclone

Advanced Features

Altera devices offer on-chip PLL features previously found only in high-end discrete PLL devices. These

advanced features, including gated lock, clock switchover, dynamic reconfiguration, programmable bandwidth,

reconfigurable bandwidth, spread spectrum clocking, and post-scale counter cascading, increase system and

device performance and provide advanced clock interfacing. The following sections define each advanced

feature, and describe its application, and the parameter settings you must select in the ALTPLL parameter

editor to enable the feature.

Advanced Control Signals (pllena, areset, pfdena)

You can use these three signals—

pllena

,

areset

, and

pfdena

—to observe and control PLL operation and

resynchronization.

pllena

Use the

pllena

signal to enable or disable the PLL. When you deassert the

pllena

signal, the PLL does not

drive any output clock signal and therefore it loses lock. All counters in the PLL, including the gated lock

counter, return to the default state. When you assert the

pllena

signal, the PLL drives output clock signals

and tries to gain lock. The single PLL enable port on each device is shared among all PLLs on the device. By

default, the

pllena

signal is tied to VCC internally.

areset

The

areset

signal is the reset or resynchronization input for each PLL. The device input pin or internal

logic can drive the

areset

signal. When you assert the

areset

signal, all counters in the PLL, including the

gated lock counter, are reset to initial values, in which the PLL output is cleared and the PLL is in the out-

of-lock state. The VCO is also reset to its nominal setting. When the

areset

signal is deasserted, the PLL

resynchronizes its input and tries to gain lock.

(1)

Only four ports can be used as the external clock output ports.

(2)

Only one port can be used as the external clock output port.

ALTPLL (Phase-Locked Loop) IP Core User Guide

Altera Corporation

ug-altpll

Advanced Features

12

2014.08.18