Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 24

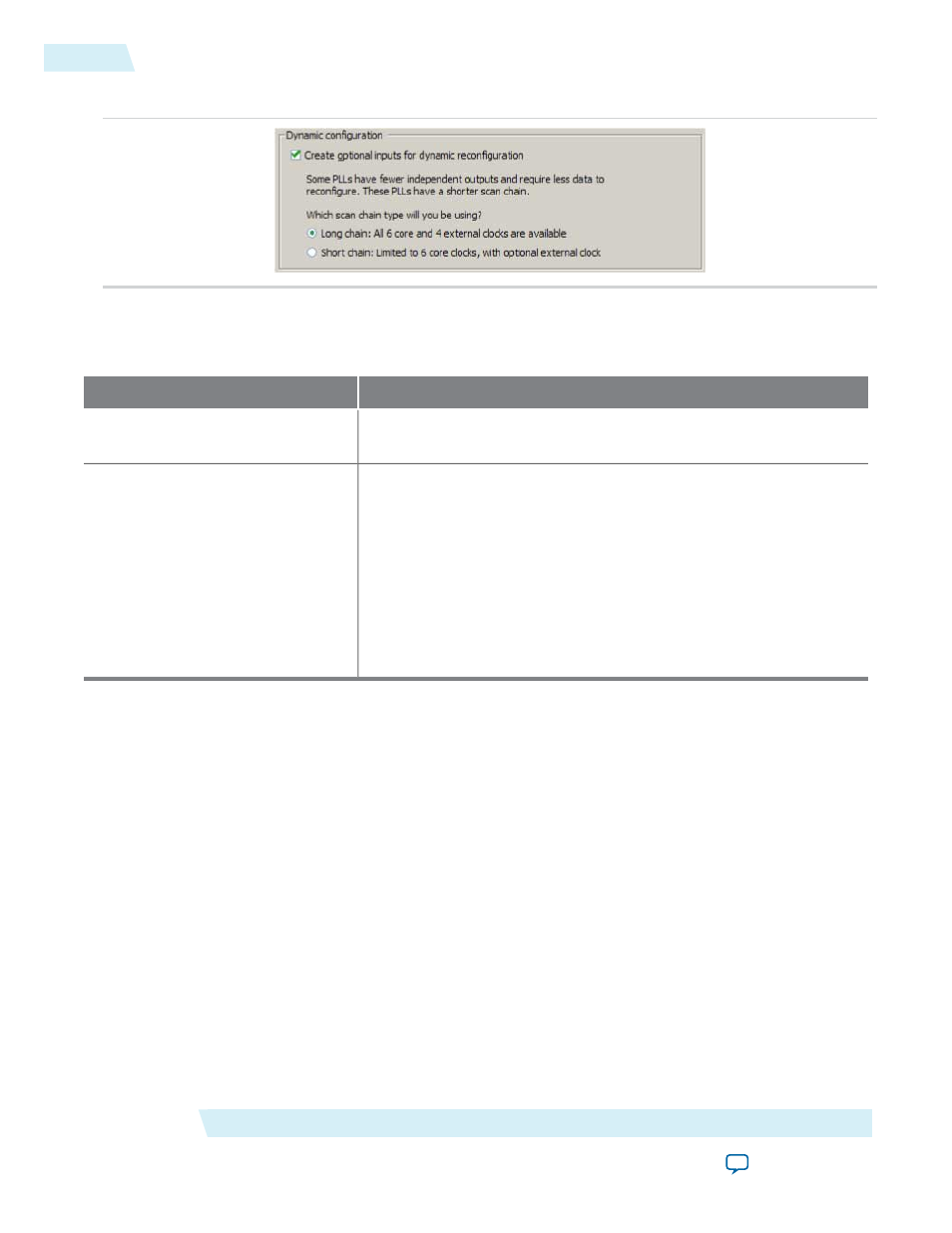

Figure 16: Dynamic Reconfiguration Options for Stratix and Stratix GX Devices

The following table lists the dynamic reconfiguration options using scan chains.

Table 12: Dynamic Reconfiguration Options for Stratix and Stratix GX Devices

Description

Option

This option enables all the PLL reconfiguration ports for this instantia-

tion—

scanclk

,

scanaclr

,

scandata

, and

scandataout

.

Create optional inputs for dynamic

reconfiguration

This option lets you specify the following types of scan chain to be used

in the PLL reconfiguration:

• Long chain—Specifies that you are using PLLs 5 and 6 with PLL

reconfiguration. PLLs 5 and 6 have six logic array outputs and four

external clock outputs and therefore, have a longer reconfiguration

chain.

• Short chain—Specifies that you are using PLLs 11 and 12 with PLL

reconfiguration. PLLs 11 and 12 have only six logic array outputs

with no dedicated external clock output counters and are considered

the shorter reconfiguration chain PLLs.

Which scan chain type will you be

using?

For devices that use the normal dynamic reconfiguration scheme, the parameter settings are located on the

PLL Reconfiguration page of the ALTPLL parameter editor.

The following figure shows the normal dynamic configuration scheme options that uses configuration files.

ALTPLL (Phase-Locked Loop) IP Core User Guide

Altera Corporation

ug-altpll

Parameter Settings

24

2014.08.18