Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 42

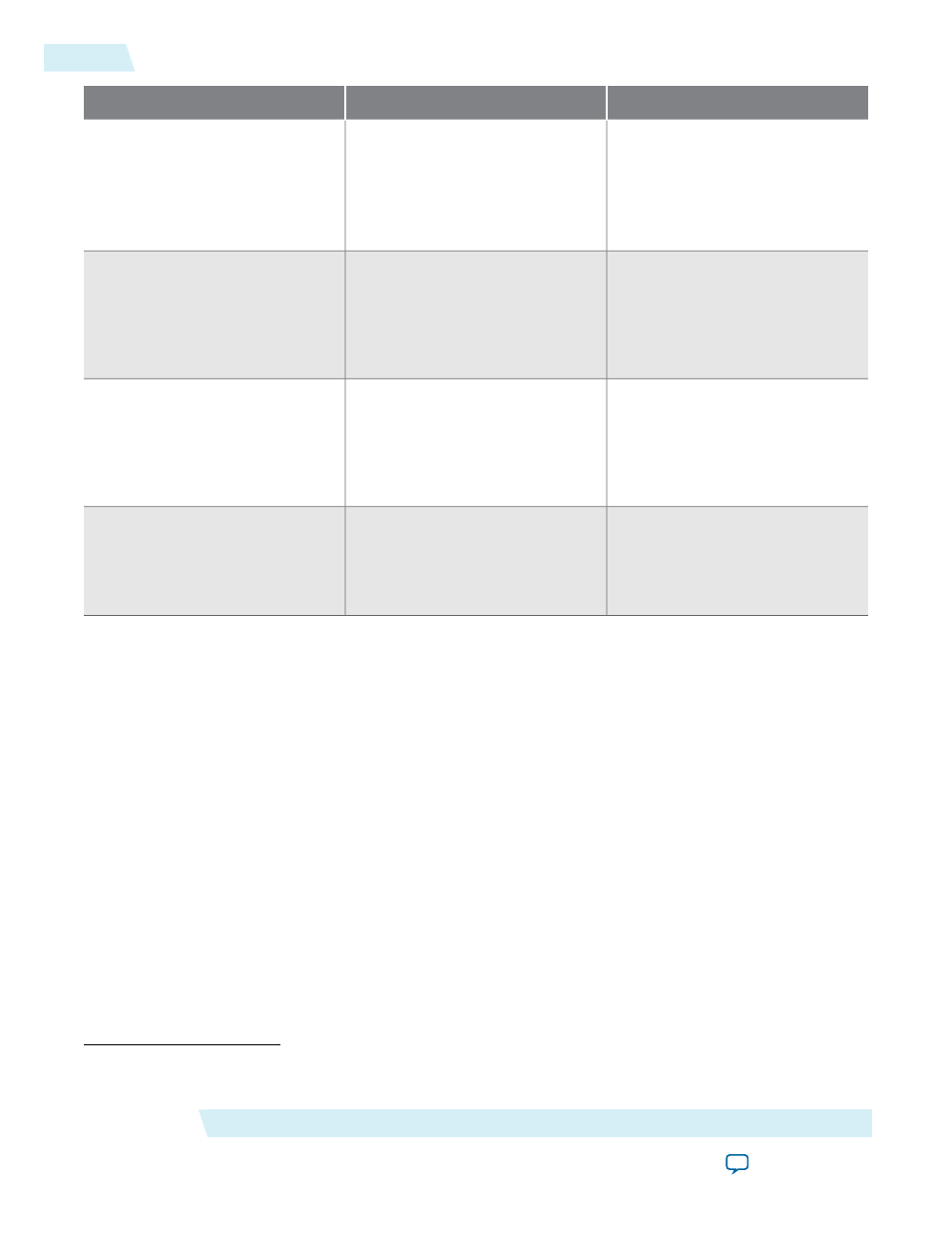

Description

Condition

Port Name

(7)

clkbad1

and

clkbad0

ports check

for input clock toggling. If the

inclk0

port stops toggling, the

clkbad0

port goes high. If the

inclk1

port stops toggling, the

clkbad1

port goes high.

Optional

clkbad[]

This output port acts as an

indicator when the clock

switchover circuit initiates. Only

available for Arria GX, HardCopy

II, Stratix, Stratix GX, Stratix II,

and Stratix II GX devices.

Optional

clkloss

Enable pulse output port. This

port is available only when the

PLL is in LVDS mode. Only

available for Arria GX, HardCopy

II, Stratix II, and Stratix II GX

devices.

Optional

enable[]

The clock output of the PLL that

feeds the dedicated clock pins on

the device. Only available for

Cyclone, Stratix, and Stratix GX

devices.

Optional

e[]

(7)

Replace the brackets,

[]

, in the port name with an integer to get the exact name (for example,

c0

,

c1

,

c3

,

e0

,

e1

,

e2

,

enable1

and

sclkout0

).

ALTPLL (Phase-Locked Loop) IP Core User Guide

Altera Corporation

ug-altpll

ALTPLL Output Ports

42

2014.08.18