Summary of spread-spectrum clocking feature, Gated lock and self-reset, Gated lock – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 18

The modulation frequency, often called sweep rate, defines how fast the spreading signal sweeps from the

minimum to the maximum frequency.

Turning on spread-spectrum clocking creates no new top-level ports.

Summary of Spread-Spectrum Clocking Feature

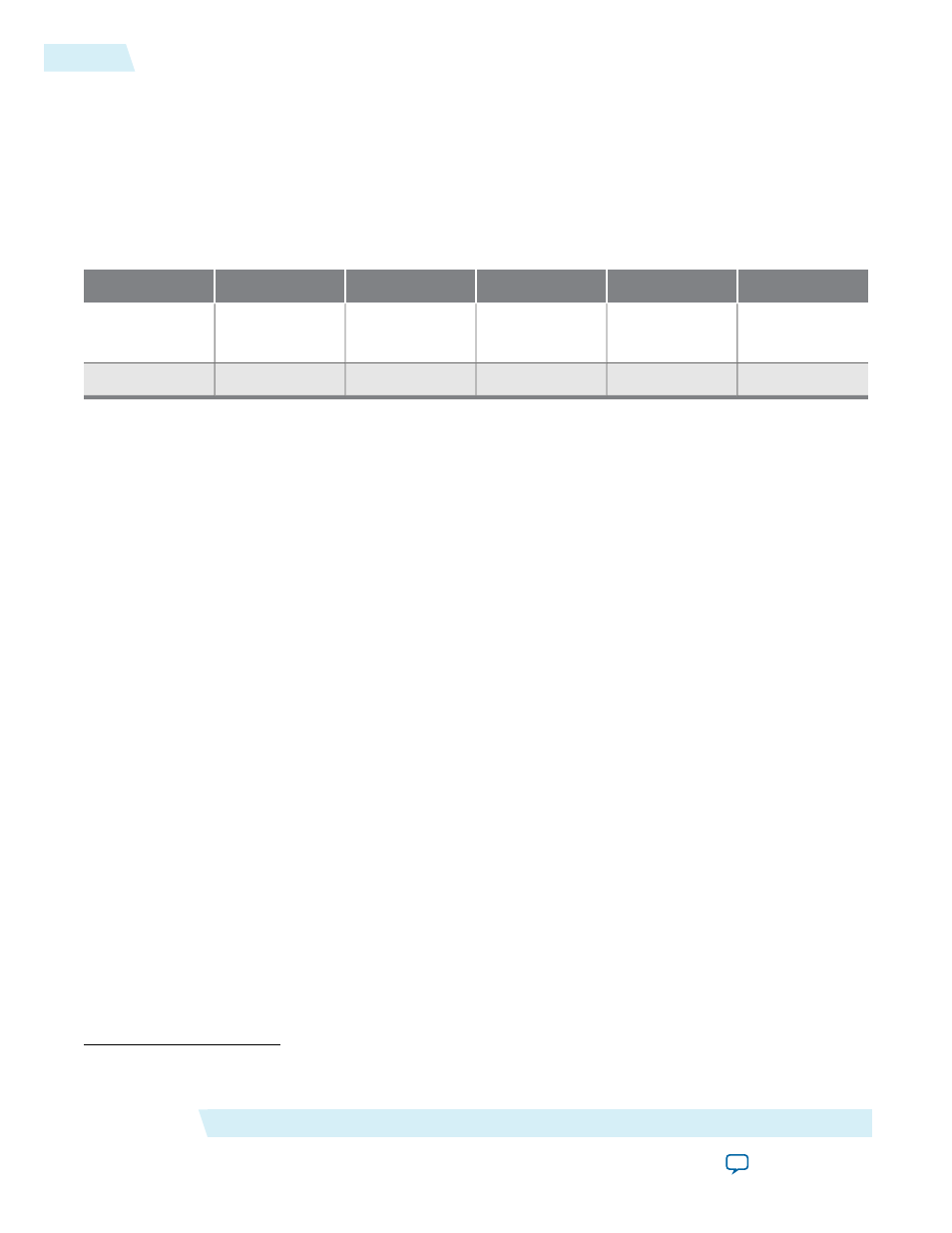

The following table summarizes the PLL types that support the spread-spectrum clocking feature.

Table 9: Spread-Spectrum Clocking Feature

Cyclone Series PLL

Fast PLL

Enhanced PLL

Left_Right

Top_Bottom

Device

—

—

—

Yes

(3)

Yes

(3)

Stratix IV

No

—

—

—

—

Cyclone IV

Gated Lock and Self-Reset

The lock time of a PLL is defined as the amount of time required by the PLL to attain the target frequency

and phase relationship after device power-up, after a change in the PLL output frequency, or after resetting

the PLL.

A PLL might lose lock for a number of reasons, such as the following causes:

• Excessive jitter on the input clock.

• Excessive switching noise on the clock inputs of the PLL.

• Excessive noise from the power supply can cause high output jitter and possible loss of lock.

• A glitch or stopping of the input clock to the PLL.

• Resetting the PLL by asserting the

areset

or

pllena

ports of the PLL.

• An attempt to reconfigure the PLL might cause the M counter, N counter, or phase shift to change, which

causes the PLL to lose lock. However, changes to the post-scale counters do not affect the PLL locked

signal.

• PLL input clock frequency drifts outside the lock range specification.

• The PFD is disabled using the

pfdena

port. When this happens, the PLL output phase and frequency

tend to drift outside of the lock window.

The ALTPLL IP core allows you to monitor the PLL locking process using a lock signal named

locked

and

also allows you to set the PLL to self-reset on loss of lock.

Gated Lock

Some devices support a gated lock signal that allows you to configure a programmable 20-bit counter that

holds the lock signal low for a user-specified number of input clock transitions. This is useful to eliminate

the false toggling of the lock signal as the PLL begins tracking the reference clock. Gated lock allows the PLL

to lock before asserting the

locked

signal, providing a stabilized lock signal.

An asserted

locked

signal indicates the PLL clock output is aligned with the PLL reference input clock. The

locked

signal might toggle as the PLL begins tracking the reference clock. To avoid such a false lock indication,

(3)

This device can accept a spread-spectrum input with typical modulation frequencies, but it cannot generate

spread-spectrum clock signals internally.

ALTPLL (Phase-Locked Loop) IP Core User Guide

Altera Corporation

ug-altpll

Summary of Spread-Spectrum Clocking Feature

18

2014.08.18