Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 15

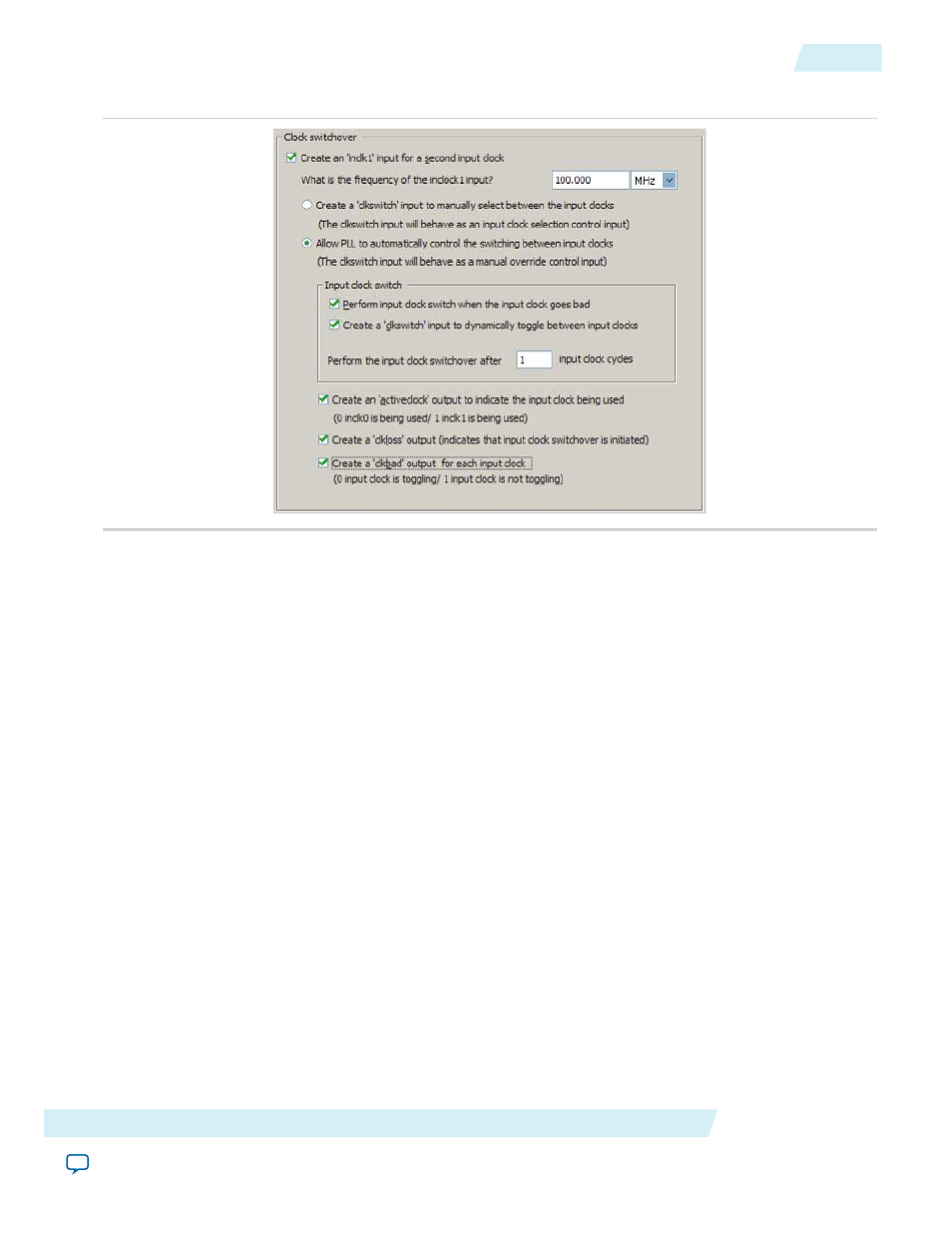

Figure 9: Clock Switchover

To enable the switchover feature, turn on Create an 'inclk1' input for a second input clock, and specify the

frequency of the

inclk1

signal. The

inclk0

signal is by default the primary input clock signal of the ALTPLL

IP core.

Select the related option for manual or automatic clock switchover mode. For the automatic clock switchover

mode, you can choose to create the

clkswitch

signal as a manual override. The automatic switchover is

initiated during loss of lock or when the

inclk0

signal stops toggling or when the

clkswitch

signal is

asserted. You must specify the number of clock cycles to wait before the PLL performs the clock switchover.

Note that the allowed number of clock cycles to wait is device-dependant.

You can use the optional signals –

activeclock

,

clkloss

, and

clkbad

—as indicators when you use the

clock switchover feature.

Use the

activeclock

signal to monitor which input clock signal is driving the PLL. When the current clock

signal is

inclk0

, the

activeclock

signal is low. When the current clock signal is

inclk1

, the

activeclock

signal is high.

Use the

clkbad

signals (

clkbad0

and

clkbad1

) to monitor which input clock signal has stopped toggling.

The

clkbad0

signal is used to monitor the

inclk0

signal, and the

clkbad1

signal monitors the

inclk1

signal.

The

clkbad0

signal goes high when the

inclk0

signal stops toggling, and the

clkbad1

signal goes high when

the

inclk1

signal stops toggling. The

clkbad

signals remain low when the input clock signals are toggling.

Use the

clkloss

signal to monitor the current status of the clock switchover. The

clkloss

signal goes high

to indicate that loss of lock has been detected, and the clock switchover is initiated. The

clkloss

signal

remains low when the clock switchover is not initiated. The

clkloss

signal is only available in Arria GX,

Stratix, Stratix GX, Stratix II, and Stratix II GX devices.

The following top-level ports are created from these parameter settings:

• Input ports:

inclk1

and

clkswitch

.

• Output ports:

activeclock

,

clkloss

,

clkbad0

, and

clkbad1

.

Altera Corporation

ALTPLL (Phase-Locked Loop) IP Core User Guide

15

Parameter Settings

ug-altpll

2014.08.18