Altpll output ports – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 41

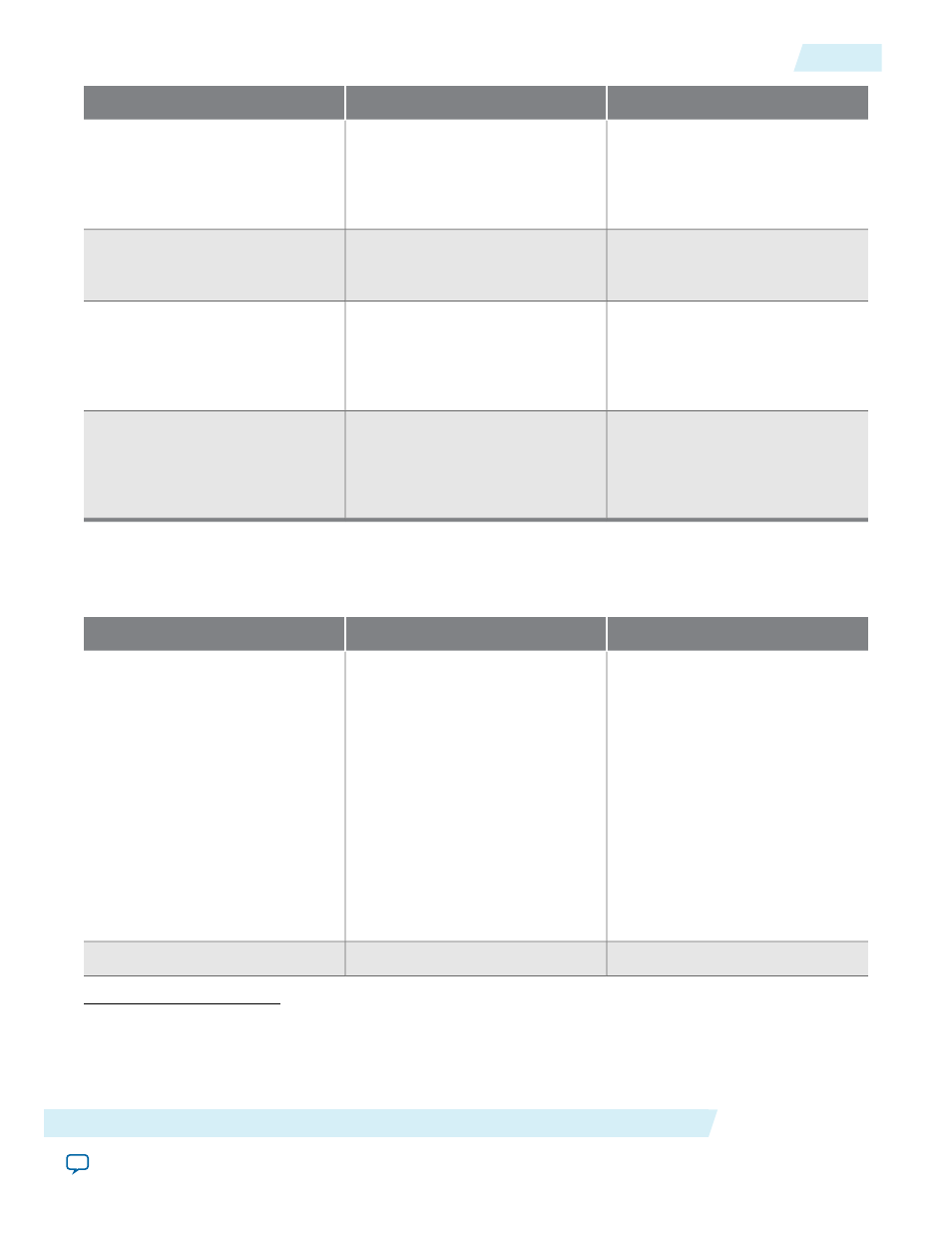

Description

Condition

Port Name

(6)

Clock enable port for the serial

scan chain. Available only for

Arria II GX, Cyclone III,

HardCopy III, and Stratix III

devices onwards.

Optional

scanclkena

Contains the data for the serial

scan chain. Not available for

Cyclone and Cyclone II devices.

Optional

scandata

Port that controls the serial scan

chain to read input from the

scandata

port. Only available for

Arria GX, HardCopy II, Stratix II,

and Stratix II GX devices.

Optional

scanread

Port that controls the real-time

programming scan chain to write

to the PLL. Only available for

Arria GX, HardCopy II, Stratix II,

and Stratix II GX devices.

Optional

scanwrite

ALTPLL Output Ports

Table 17: ALTPLL Output Ports

Description

Condition

Port Name

(7)

Specifies which clock is used as the

primary reference clock when the

clock switchover circuit initiates.

If the

inclk0

is in use, the

activeclock

port goes low. If the

inclk1

is in use, the

activeclock

port goes high.

You can set the PLL to automati-

cally initiate the clock switchover

when the primary reference clock

is not toggling correctly, or you

can manually initiate the clock

switchover using the

clkswitch

input port.

Optional

activelock

The clock output of the PLL.

Required

c[]

(6)

Replace brackets, [], in the port name with integer to get the exact name. For example,

inclk0

,

inclk1

,

c1_

ena

, and

e0_ena

.

(7)

Replace the brackets,

[]

, in the port name with an integer to get the exact name (for example,

c0

,

c1

,

c3

,

e0

,

e1

,

e2

,

enable1

and

sclkout0

).

Altera Corporation

ALTPLL (Phase-Locked Loop) IP Core User Guide

41

ALTPLL Output Ports

ug-altpll

2014.08.18