Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 51

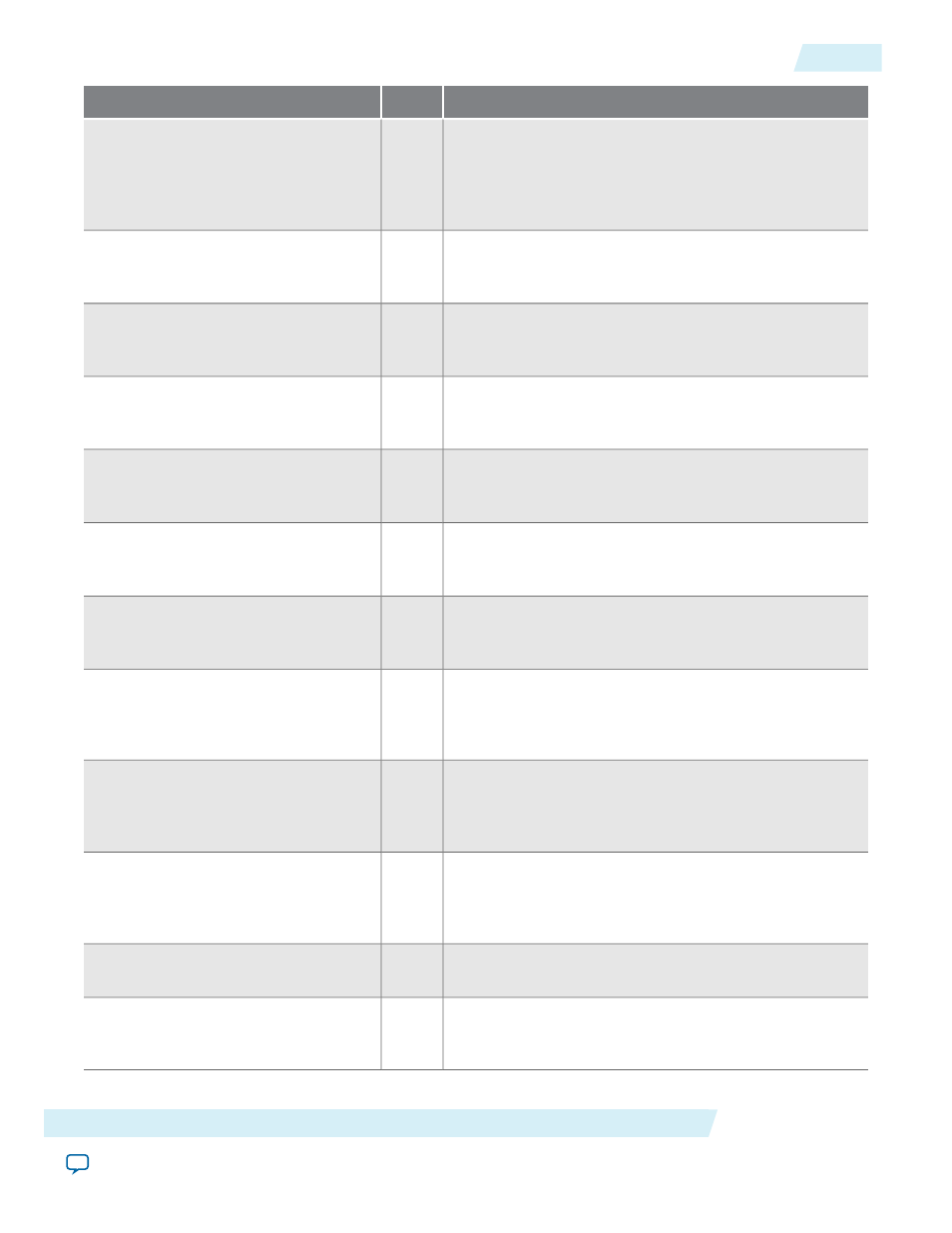

Description

Type

Parameter

Specifies which clock output has a board-level connection

to the

fbin

port. If the

OPERATION_MODE

parameter is set

to

EXTERNAL_FEEDBACK

, the

FEEDBACK_SOURCE

parameter

is needed. Values are

EXTCLK[]

. If omitted, the value is

EXTCLK0

.

String

FEEDBACK_SOURCE

Specifies the high period count for the corresponding

G[3..0

] counter. Values range from

1

to

512

. If omitted,

the default is

1

.

Integer

G[]_HIGH

Specifies the initial value for the corresponding G[3..0]

counter. Values range from

1

to

512

. If omitted, the default

is

1

.

Integer

G[]_INITIAL

Specifies the low period count for the corresponding

G[3..0]

counter. Values range from

1

to

512

. If omitted,

the default is

1

.

Integer

G[]_LOW

Specifies the mode for the corresponding

G[3..0]

counter.

Values are

BYPASS

,

ODD

, or

EVEN

. If omitted, the default is

BYPASS

.

String

G[]_MODE

Specifies the phase tap for the corresponding

G[3..0]

counter. Values range from

0

to

7

. If omitted, the default

is

0

.

Integer

G[]_PH

Specifies, in nanoseconds (ns), the time delay for the

corresponding

G[3..0]

counter. Values range from

0

ns

to

3

ns. If omitted, the default is

0

.

String

G[]_TIME_DELAY

Specifies the value for the 20-bit counter that gates the

locked

output port before sending it to the

locked

port.

This parameter is required for simulation in third-party

simulators.

Integer

GATE_LOCK_COUNTER

Specifies whether the

locked

port should be gated

internally with a 20-bit programmable counter so it does

not oscillate during initial power-up. Values are

NO

or

YES

.

If omitted, default is

NO

.

String

GATE_LOCK_SIGNAL

Specifies the input frequency for the input clock port,

inclk[1..0]

. The compiler uses the frequency of the

clk0

port to calculate the PLL parameters, but also analyzes and

reports the phase shifts for the

clk1

port.

Integer

INCLK[]_INPUT_FREQUENCY

This parameter is used for modeling and behavioral

simulation purposes. The default is

NONE

String

INTENDED_DEVICE_FAMILY

Specifies the scaling factor, in half-clock cycles, for which

the clock output ports must be out-of-lock before the

locked

pin goes low.

Integer

INVALID_LOCK_MULTIPLIER

Altera Corporation

ALTPLL (Phase-Locked Loop) IP Core User Guide

51

ALTPLL Parameters

ug-altpll

2014.08.18