Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 48

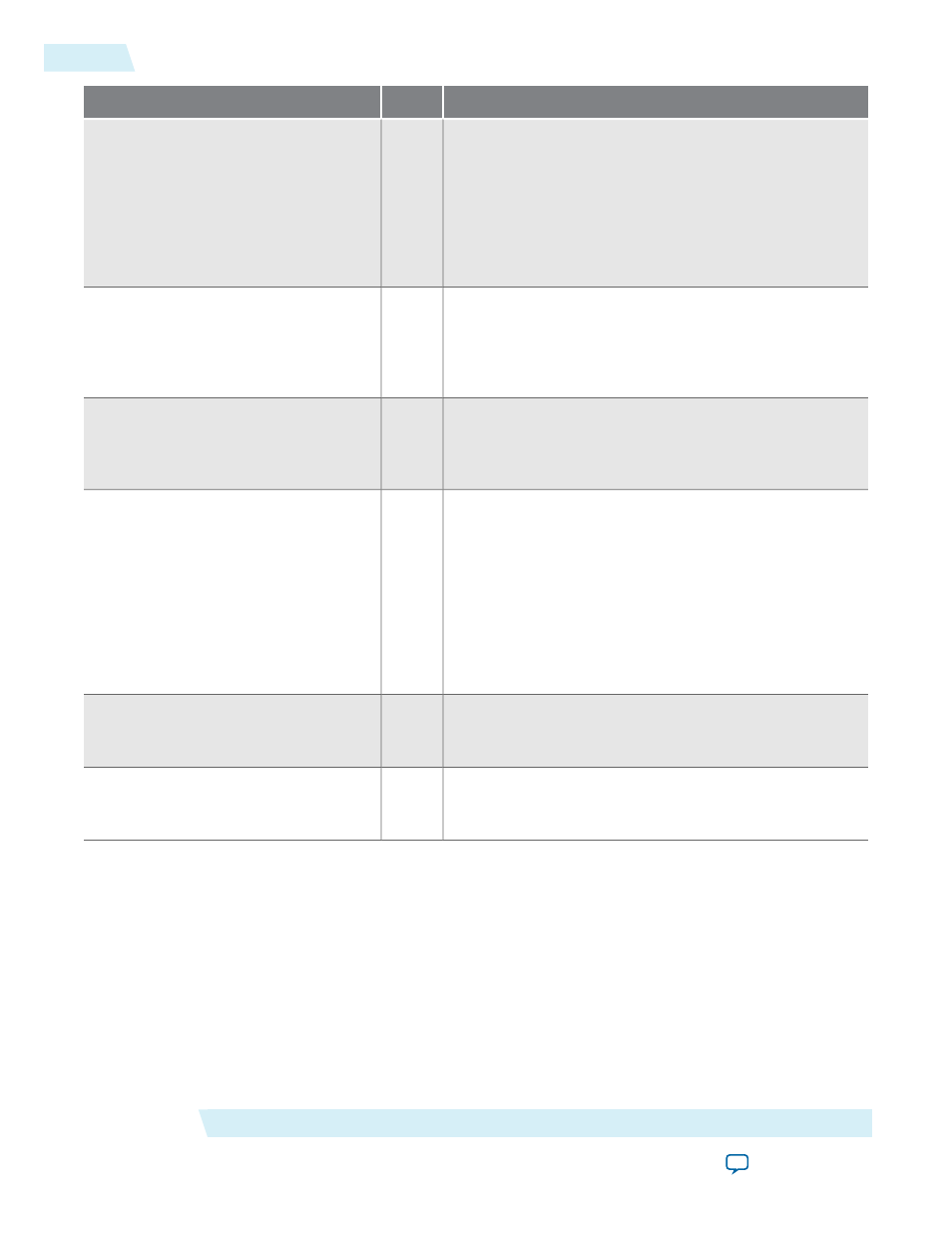

Description

Type

Parameter

Specifies the integer multiplication factor for the VCO

frequency for the corresponding output clock port,

CLK[9..0]

. The parameter value must be greater than

0

.

Specify this parameter only if the corresponding

CLK[9..0

]

port is used; however, it is not required if a Clock Settings

assignment is specified for the corresponding

CLK[9..0]

port. If omitted, the default is

0

. Parameters

CLK[9..5]_

MULTIPLY_BY

are not available in Cyclone III devices.

Integer

CLK[]_MULTIPLY_BY

Specifies the output frequency of the corresponding output

clock port,

CLK[9..0]

.This parameter is ignored if the

corresponding

CLK[9..0]

port is not used. This parameter

is unavailable if multiplication or division factors are

specified. If omitted, the default is

0

.

Integer

CLK[]_OUTPUT_FREQUENCY

Specifies the phase shift for the corresponding output clock

port,

CLK[9..0]

, in picoseconds (ps). If omitted, the default

is

0

. Parameters

CLK[9..5]_PHASE_SHIFT

are not available

in Cyclone III devices.

String

CLK[]_PHASE_SHIFT

Specifies, in picoseconds (ps), the delay value to be applied

to the corresponding output clock port,

CLK[9..0]

. This

parameter affects only the corresponding

CLK[9..0]

port

and is independent of the corresponding

CLK[9..0]_

PHASE_SHIFT

parameter; therefore, both parameters can

be used simultaneously. If no units are specified, default

is picoseconds (ps). Legal time delay values range from -3

ns to 6 ns in increments of 0.25 ns. These values should

not be used as parameters except when reprogramming

the PLL using the real-time programming interface.

String

CLK[]_TIME_DELAY

Specifies whether the clock output needs to be forced to

use even counter mode for the corresponding

CLK[9..0]

port. Values are

ON

or

OFF

. If omitted, the default is

OFF

.

String

CLK[]_USE_EVEN_COUNTER_MODE

Specifies whether the clock output needs to be forced to

use even counter values for the corresponding

CLK[9..0]

port. Values are

ON

or

OFF

. If omitted, the default is

OFF

.

String

CLK[]_USE_EVEN_ COUNTER_VALUE

ALTPLL (Phase-Locked Loop) IP Core User Guide

Altera Corporation

ug-altpll

ALTPLL Parameters

48

2014.08.18