Pll dynamic reconfiguration, Parameter settings – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 23

The parameter settings to generate output files using advanced PLL parameters are located on the

Scan/Inputs/Lock or Inputs/Lock page of the ALTPLL parameter editor.

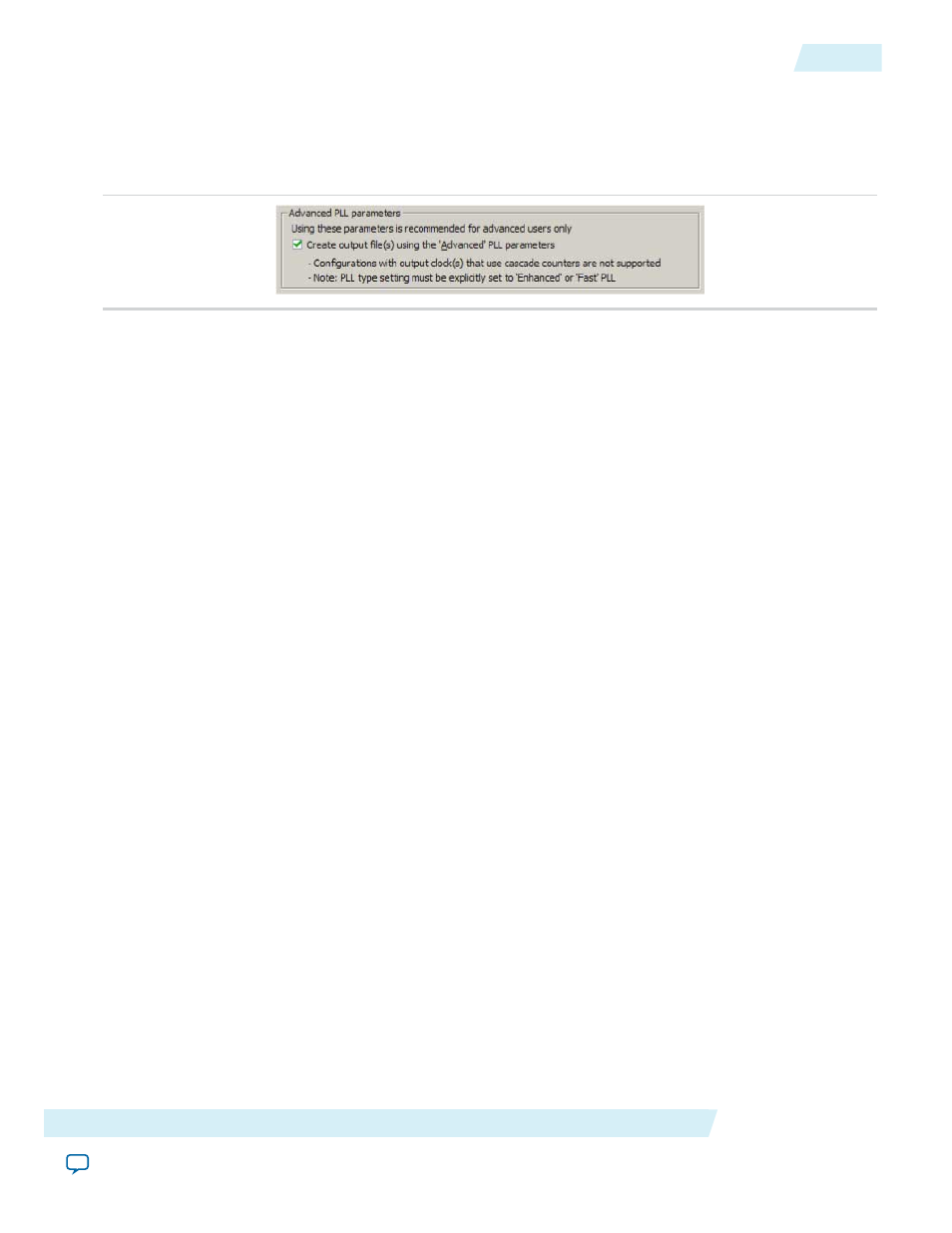

The following figure shows the Advanced PLL parameters window.

Figure 15: Advanced PLL Parameters

Turn on Create output file(s) using the 'Advanced' PLL parameters to enable the feature. You must

explicitly select enhanced or fast PLL to use this option.

When this option is turned on, the generated output files contain all of the initial counter values used in the

PLL. You can use these values for functional simulation in a third-party simulator.

These parameter settings create no additional top-level ports.

PLL Dynamic Reconfiguration

The PLL Dynamic Reconfiguration feature allows you to reconfigure your PLL on-the-fly. You can control

the configuration process using the following ports:

• Input ports:

scanclk

,

scandata

,

scanclkena

, and

configupdate

.

• Output ports:

scandataout

and

scandone

. The

scandone

port is not available for Cyclone, Cyclone II,

Stratix, and Stratix GX devices.

The Stratix and Stratix GX enhanced PLLs can be dynamically reconfigured using scan chains. Depending

on the PLL type, two options are available for the scan chain – long or short. The long scan chain allows the

configuration of those PLLs with six core and four external clocks, while the short scan chain limits the

configuration to those PLLs with the six core clocks with no external clocks.

The scan chain method for dynamic reconfiguration is not available for all supported device families. The

devices that support the normal dynamic reconfiguration scheme uses configuration files, such as the

Hexadecimal-format file, .hex, or the Memory Initialization file, .mif. These files are used together with the

ALTPLL_RECONFIG IP core to perform the dynamic configuration.

Related Information

Parameter Settings

To enable the dynamic reconfiguration feature for Stratix and Stratix GX devices, use the parameter settings

located on the Scan/Input/Lock page of the ALTPLL parameter editor.

The following figure shows the dynamic reconfiguration options using scan chains.

Altera Corporation

ALTPLL (Phase-Locked Loop) IP Core User Guide

23

PLL Dynamic Reconfiguration

ug-altpll

2014.08.18