Dynamic phase configuration, Supported devices – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 26

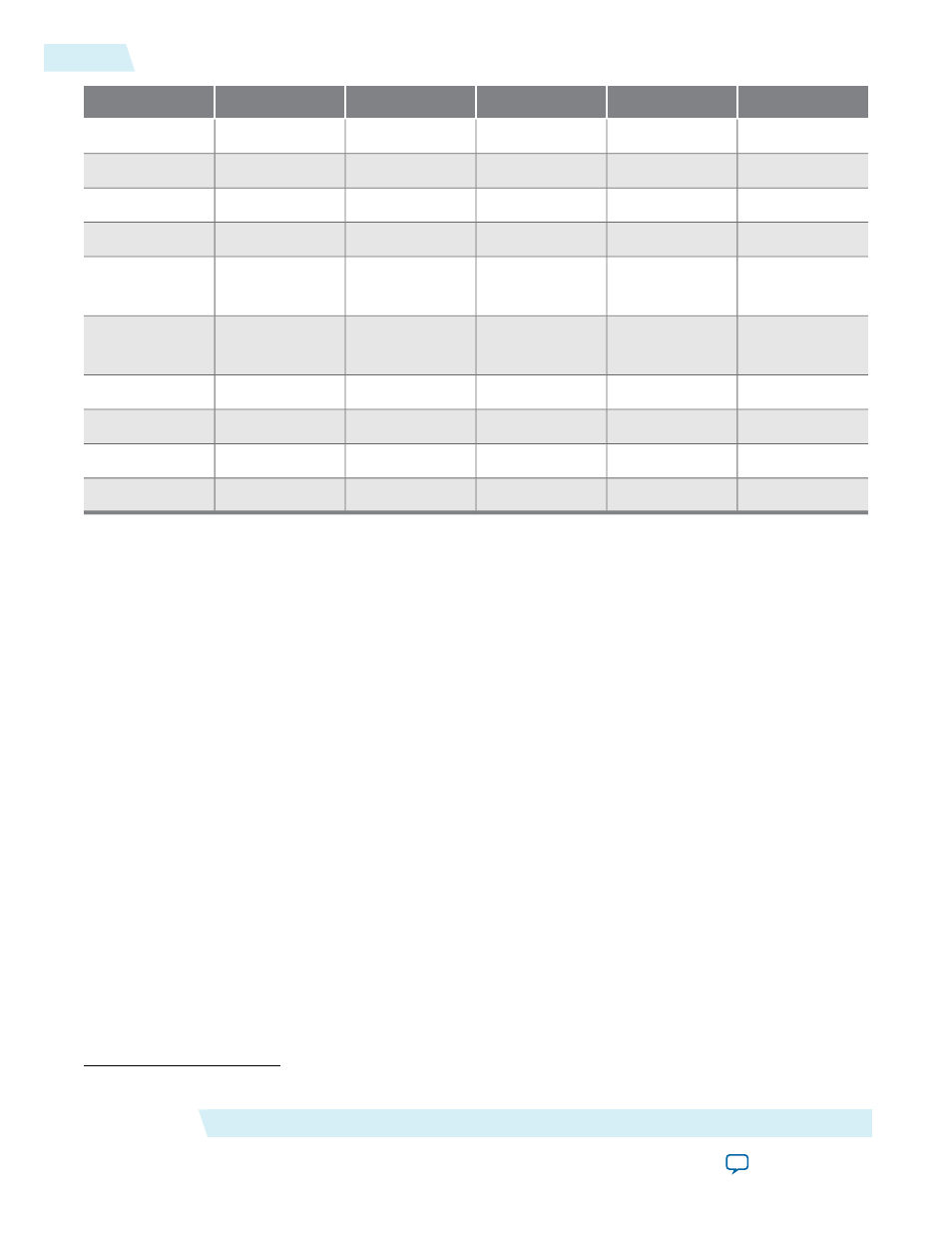

Cyclone Series PLL

Fast PLL

Enhanced PLL

Left_Right

Top_Bottom

Device Family

—

—

—

Yes

Yes

Stratix IV

—

—

—

Yes

Yes

Stratix III

—

Yes

Yes

—

—

Stratix II

—

Yes

Yes

—

—

Stratix II GX

—

No

Yes

(5)

—

—

Stratix

—

No

Yes

(5)

—

—

Stratix GX

Yes

—

—

—

—

Cyclone IV

Yes

—

—

—

—

Cyclone III

No

—

—

—

—

Cyclone II

No

—

—

—

—

Cyclone

Dynamic Phase Configuration

The dynamic phase configuration feature allows the output phases of individual PLL outputs to dynamically

adjust relative to each other and the reference clock, without sending serial data through the scan chain of

the corresponding PLL. This feature is also known as the dynamic phase stepping feature.

You can use this feature to quickly adjust the output clock phase shift in real time. This adjustment is achieved

by incrementing or decrementing the VCO phase-tap selection to a C counter or to the M counter. By default,

the phase is shifted by 1/8th of the VCO frequency at each step. However, you can easily modify the phase

shift step resolution of the individual PLL output clock using the ALTPLL parameter editor.

For dynamic phase shifting to work correctly, the PLL must have the following ports:

• Input ports:

phasecounterselect[3..0]

,

phaseupdown

,

phasestep

, and

scanclk

• Output port:

phasedone

Related Information

on page 38

This application note describes the flow for implementing phase-locked loop (PLL) reconfiguration in Stratix

III and Stratix IV devices.

Supported Devices

The dynamic phase configuration feature is available only for Cyclone IV, Cyclone III, Arria II GX, Stratix III,

and Stratix IV device families.

(5)

This device family supports dynamic reconfiguration using scan chains only.

ALTPLL (Phase-Locked Loop) IP Core User Guide

Altera Corporation

ug-altpll

Dynamic Phase Configuration

26

2014.08.18