Clock switchover, Parameter settings – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 14

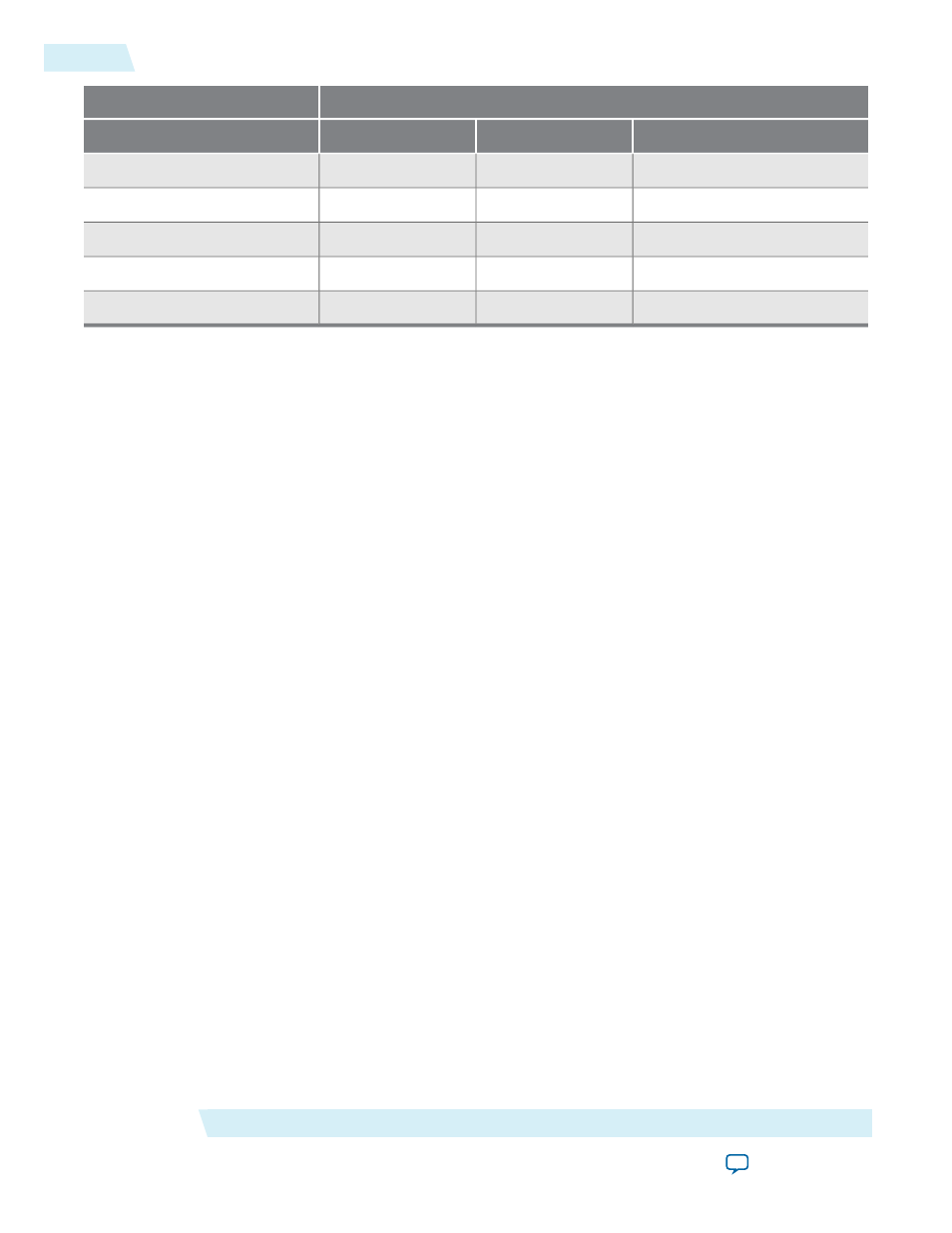

Supported Advanced Signals

Device Family

areset

pfdena

pllena

Yes

Yes

Yes

Stratix GX

Yes

Yes

—

Cyclone IV

Yes

Yes

—

Cyclone III

Yes

Yes

Yes

Cyclone II

Yes

Yes

Yes

Cyclone

Clock Switchover

The clock switchover feature allows the PLL to switch between two input clocks. The clock switchover feature

can be used for switching between clock inputs of different frequencies and is also useful for video applications

that require a manual switch between operation frequencies. The clock switchover capability is widely

implemented in telecommunication, storage, and server markets because these markets require highly reliable

clocking schemes to ensure system reliability.

The following clock switchover modes are supported by the ALTPLL IP core:

• Automatic switchover—The PLL monitors the currently used clock signal, and if it stops toggling or

loss-of-lock occurs, the PLL automatically switches to the other clock signal (

inclk0

or

inclk1

).

• Manual clock switchover—The clock switchover is controlled using the

clkswitch

signal. The manual

override feature available in automatic clock switchover is different from the manual clock switchover.

Parameter Settings

For devices that support the clock switchover feature, the parameter settings are located on the Clock

switchover page of the ALTPLL parameter editor.

The following figure shows all the options available on the Clock switchover page for an Arria GX device.

The options are device-dependent and what you see may differ.

ALTPLL (Phase-Locked Loop) IP Core User Guide

Altera Corporation

ug-altpll

Clock Switchover

14

2014.08.18