Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 39

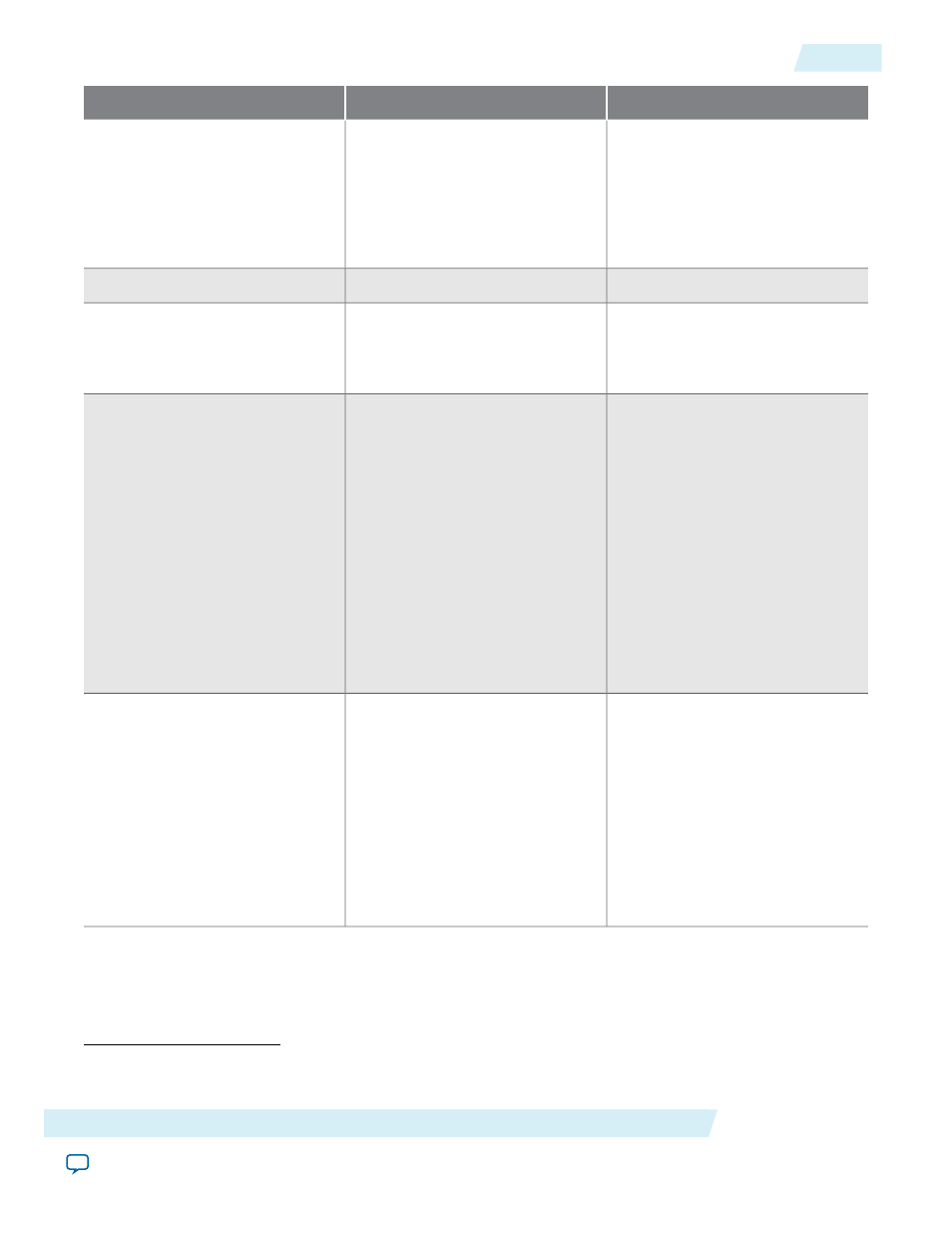

Description

Condition

Port Name

(6)

The control input port to

dynamically toggle between clock

input ports (

inclk0

and

inclk1

ports), or to manually override the

automatic clock switchover. You

should create the

clkswitch

port

if only the

inclk1

port is created.

Optional

clkswitch

Dynamic full PLL reconfiguration.

Optional

configupdate

An enable input port for the

external output clock,

e[]

.

Available for Stratix and

Stratix GX devices only.

Optional

e[]_ena[]

The external feedback input port

for the PLL.

This port must be created if the

PLL operates in the external

feedback mode. To complete the

feedback loop, there must be a

board-level connection between

the

fbin

port and the external

clock output port of the PLL.

In the Stratix III device, if the PLL

operates in the zero-delay buffer

mode and the

fbmimicbidir

port

is not used, you must connect the

fbin

port to the

fbout

port.

Optional

fbin

The clock inputs that drive the

clock network.

If more than one

inclk[]

port is

created, you must use the

clkselect

port to specify which

clock is used. The

inclk0

port

must always be connected;

connect other clock inputs if

switching is necessary. A

dedicated clock pin or PLL output

clock can drive this port.

Required

inclk[]

(6)

Replace brackets, [], in the port name with integer to get the exact name. For example,

inclk0

,

inclk1

,

c1_

ena

, and

e0_ena

.

Altera Corporation

ALTPLL (Phase-Locked Loop) IP Core User Guide

39

ALTPLL Input Ports

ug-altpll

2014.08.18