Simulating altera ip cores in other eda tools – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 33

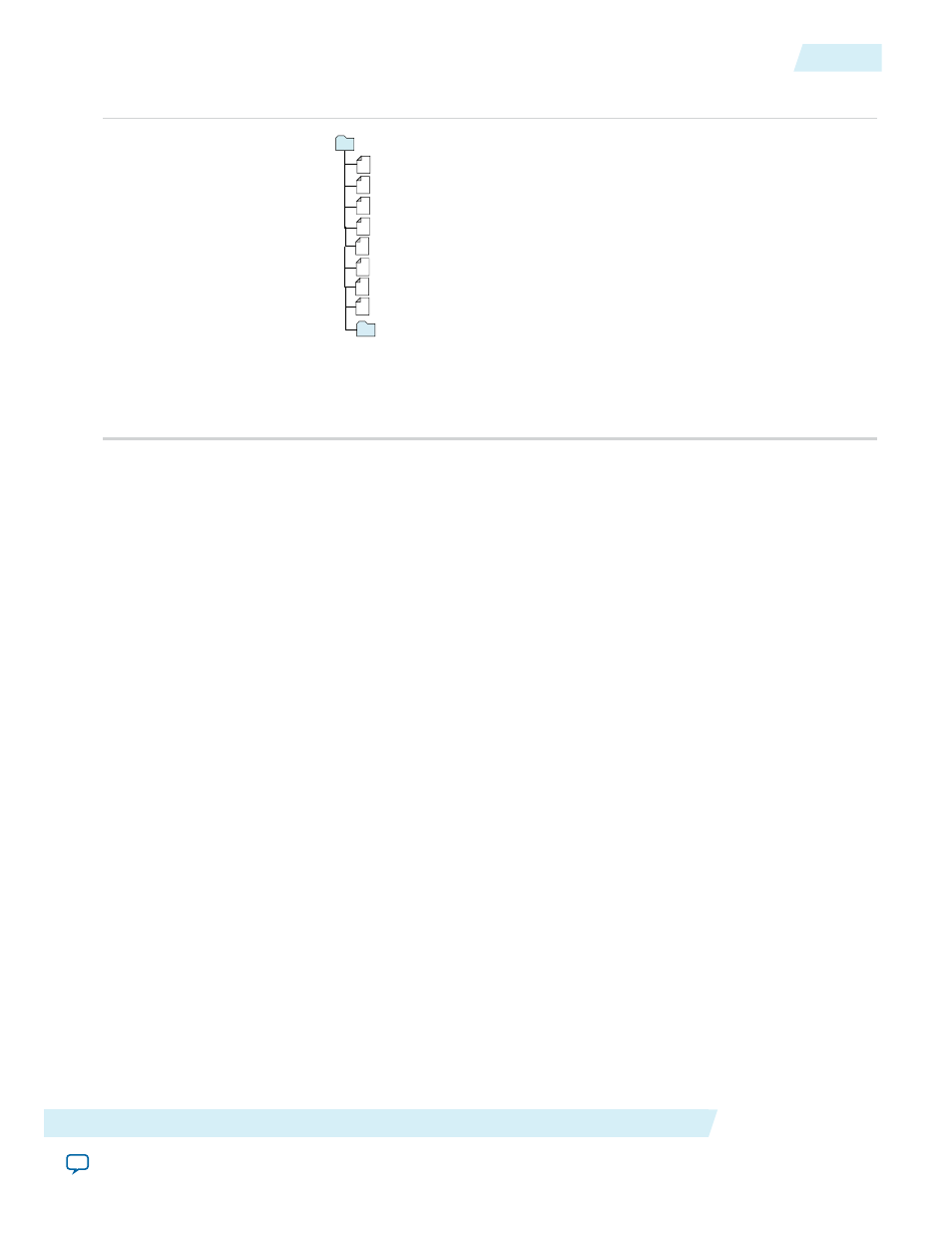

Figure 24: IP Core Generated Files

Notes:

1. If supported and enabled for your IP variation

2. If functional simulation models are generated

3. Ignore this directory

<Project Directory>

<your_ip>.v or .vhd - Top-level IP synthesis file

<your_ip>_inst.v or .vhd - Sample instantiation template

<your_ip>.bsf - Block symbol schematic file

<your_ip>.vo or .vho - IP functional simulation model 2

<your_ip>_syn.v or .vhd - Timing & resource estimation netlist1

<your_ip>_bb.v - Verilog HDL black box EDA synthesis file

<your_ip>.qip - Quartus II IP integration file

greybox_tmp

3

<your_ip>.cmp - VHDL component declaration file

Simulating Altera IP Cores in other EDA Tools

The Quartus II software supports RTL and gate-level design simulation of Altera IP cores in supported EDA

simulators. Simulation involves setting up your simulator working environment, compiling simulation

model libraries, and running your simulation.

You can use the functional simulation model and the testbench or example design generated with your IP

core for simulation. The functional simulation model and testbench files are generated in a project

subdirectory. This directory may also include scripts to compile and run the testbench. For a complete list

of models or libraries required to simulate your IP core, refer to the scripts generated with the testbench.

You can use the Quartus II NativeLink feature to automatically generate simulation files and scripts.

NativeLink launches your preferred simulator from within the Quartus II software.

Altera Corporation

ALTPLL (Phase-Locked Loop) IP Core User Guide

33

Simulating Altera IP Cores in other EDA Tools

ug-altpll

2014.08.18