Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 5

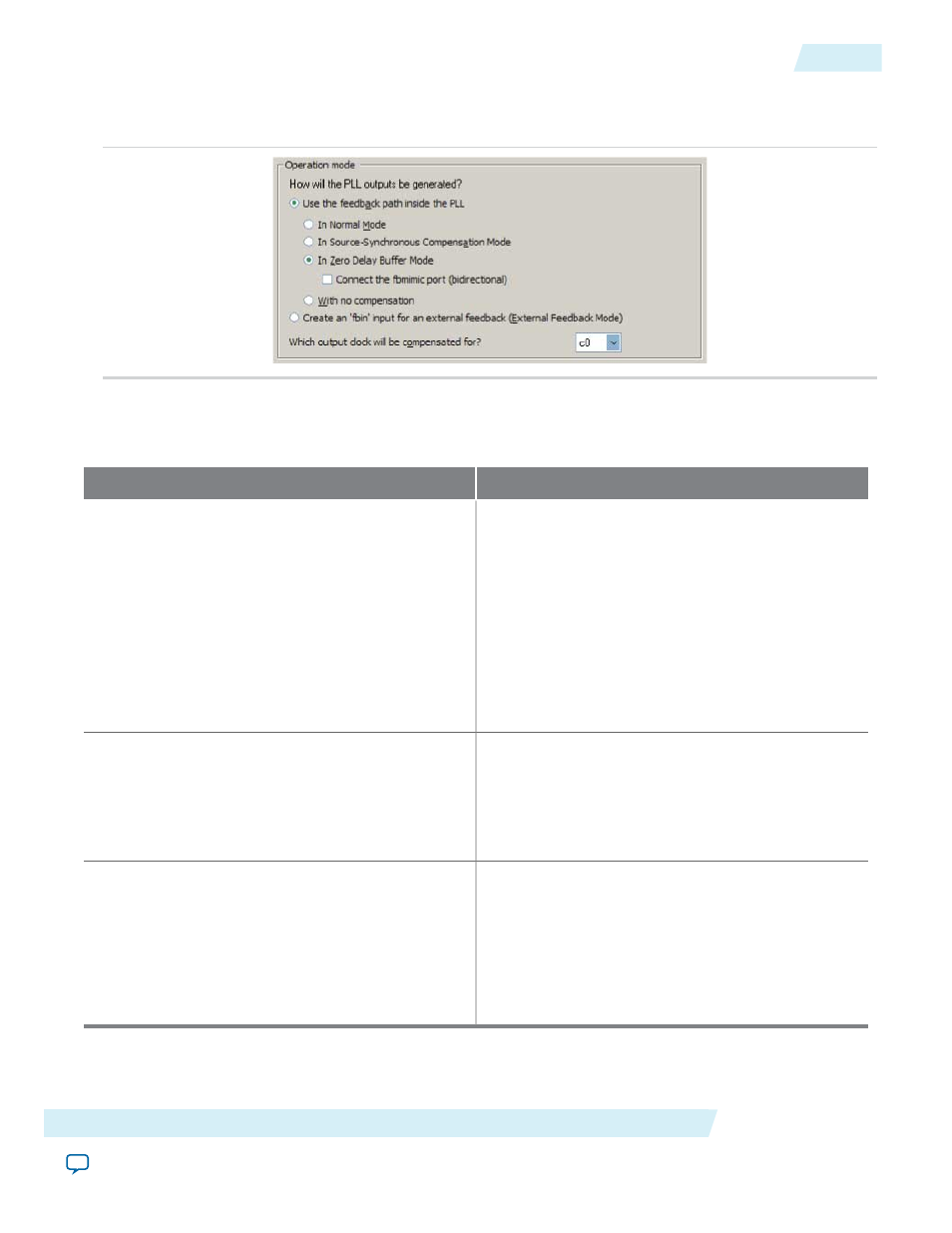

The following figure shows the options you can select from the page.

Figure 2: Operation Mode Options

The following table lists the options you can select from the page.

Table 3: Operation Mode Options and Descriptions

Description

Option

Specify which operation mode to use.

For source-synchronous mode, zero-delay buffer

mode, and external feedback mode, you must make

PLL Compensation assignments using the Assignment

Editor in addition to setting the appropriate mode in

the IP core. The assignment allows you to specify an

output pin as a compensation target for a PLL in zero-

delay buffer mode or external feedback mode, or to

specify an input pin or group of input pins as

compensation targets for a PLL in source-synchronous

mode.

Use the feedback path inside the PLL

Select this option to set the PLL in external feedback

mode. The

fbin

port is the input port to the PLL from

the external feedback path. In this mode, the PLL

compensates for the

fbin

port. The delay between the

input clock pin and the feedback clock pin is

minimized.

Create an 'fbin' input for an external feedback

(External Feedback Mode)

Specify which output port of the PLL is to be

compensated for. The drop down list contains all

output clock ports for the selected device. The correct

output clock selection depends on the operation mode

that you select. For example, for normal mode, select

the core output clock. For zero-delay buffer mode or

external feedback mode, select the external output

clock.

Which output clock will be compensated for?

The following figure shows the options you can select from the page.

Altera Corporation

ALTPLL (Phase-Locked Loop) IP Core User Guide

5

Parameter Settings

ug-altpll

2014.08.18