Design examples, Design files – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 61

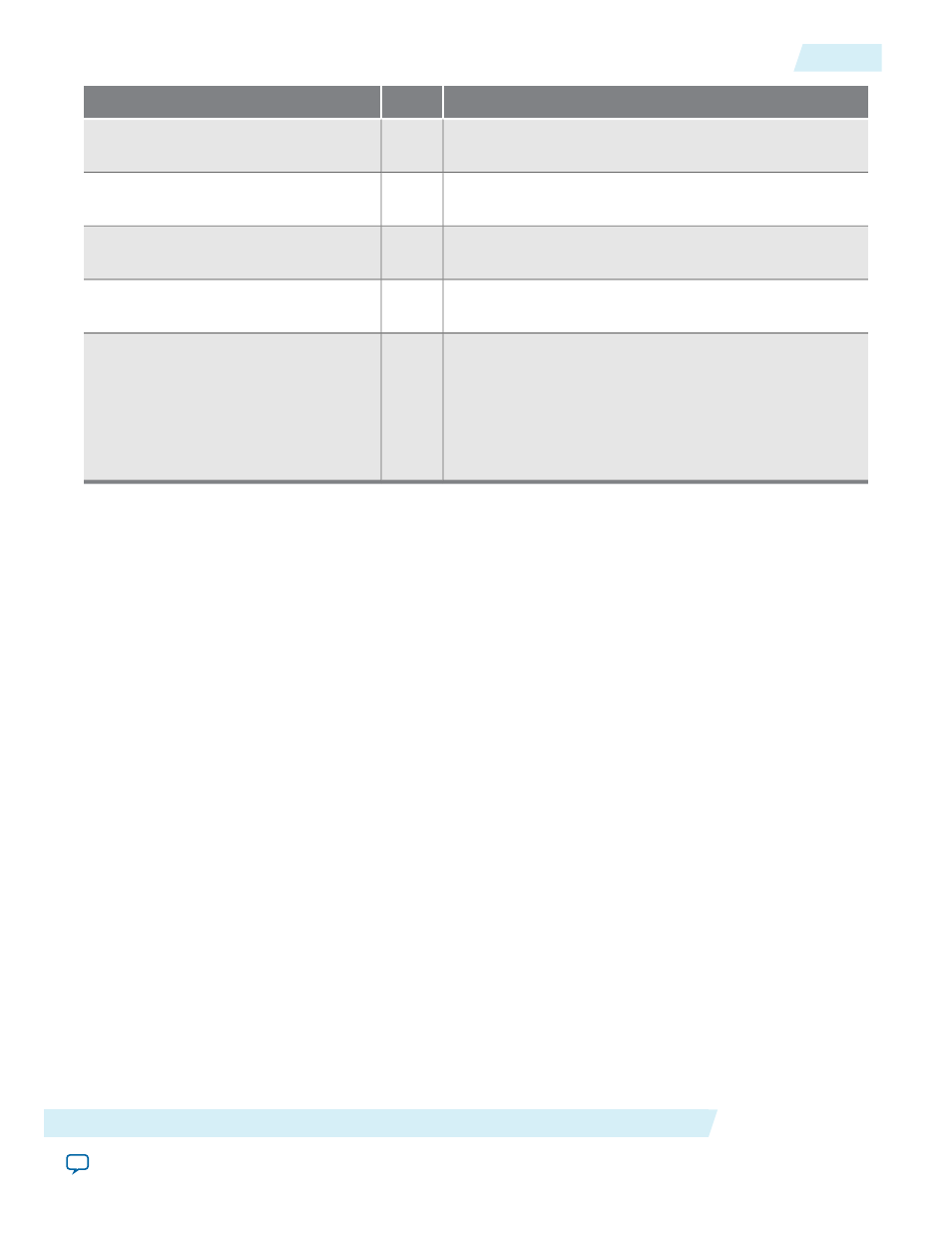

Description

Type

Parameter

Specifies the minimum value for the VCO pin. Use for

simulation purposes only.

Integer

VCO_MIN

Specifies the integer multiplication factor for the VCO pin.

If omitted, the default is

0

.

Integer

VCO_MULTIPLY_BY

Specifies the phase shift for the VCO pin. If omitted, the

default is

0

.

Integer

VCO_PHASE_SHIFT_STEP

Specifies the VCO operating range. The VCO post-scale

divider value is

1

or

2

. If omitted, the default is

1

.

Integer

VCO_POST_SCALE

Specifies the clock width. Values are

10

for Stratix III

devices,

5

for Cyclone III and Cyclone IV devices, and

6

for all other supported device families. If omitted, the

default is

6

. For Stratix III, Stratix IV, Cyclone III, and

Cyclone IV devices, the

WIDTH_CLOCK

parameter is required

for both clear box and non-clear box implementation to

reflect the correct width.

Integer

WIDTH_CLOCK

Related Information

•

on page 38

•

on page 41

•

on page 46

Design Examples

The design examples use the ALTPLL IP core to:

• Generate an external differential clock from an enhanced PLL.

• Generate and modify internal clock signals.

These examples use the IP Catlog and parameter editor. When you complete the examples, you can

incorporate them into your projects.

Related Information

•

Design Example 1: Differential Clock

on page 62

•

Design Example 2: Generating Clock Signals

on page 64

Design Files

The design files are available on the Literature and Technical Documentation page of the Altera website.

Related Information

•

Altera Corporation

ALTPLL (Phase-Locked Loop) IP Core User Guide

61

Design Examples

ug-altpll

2014.08.18