Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 40

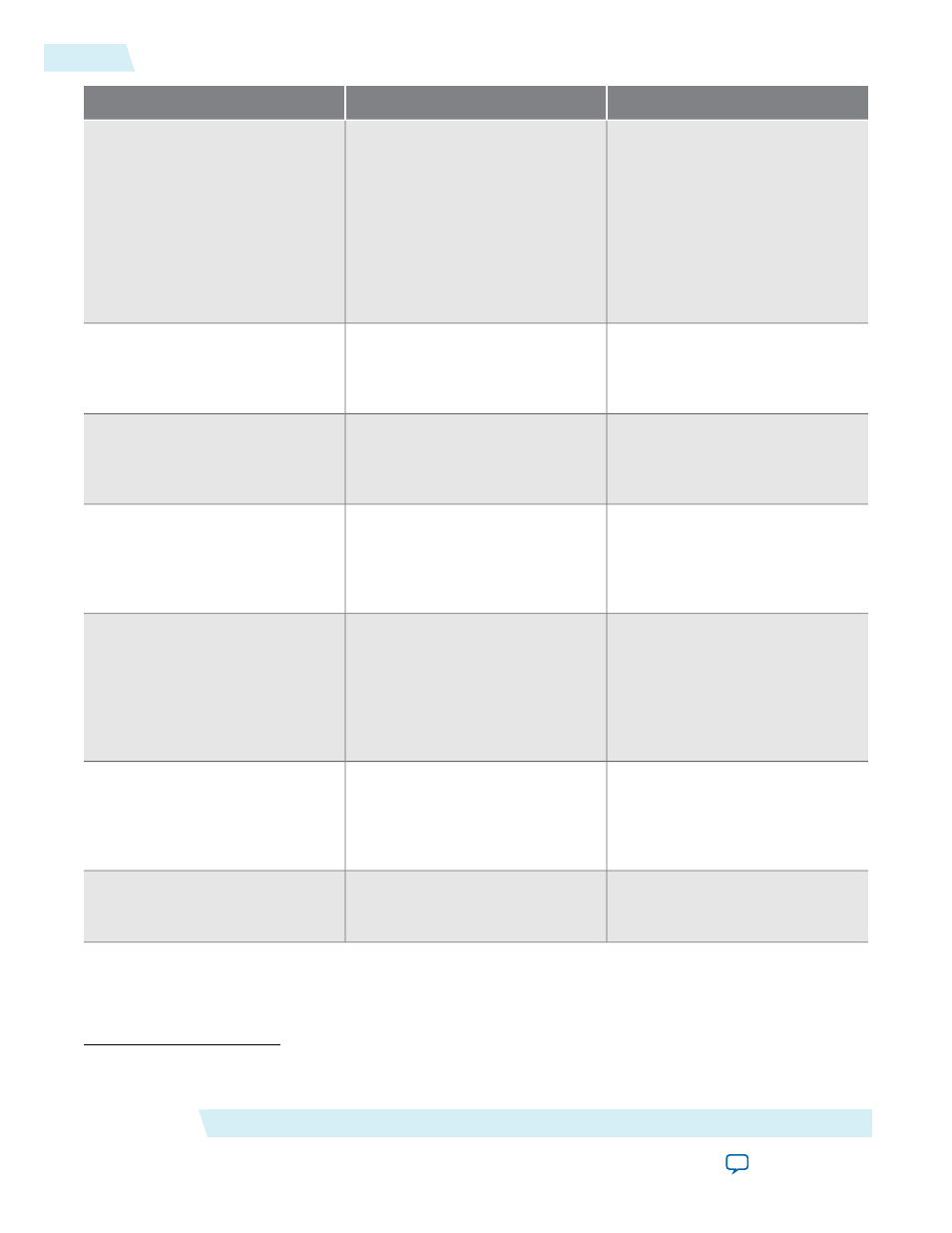

Description

Condition

Port Name

(6)

Enables the phase frequency

detector (PFD). When the PFD is

disabled, the PLL continues to

operate regardless of the input

clock. Because the PLL output

clock frequency does not change

for some time, you can use the

pfdena

port as a shutdown or

cleanup function when a reliable

input clock is no longer available.

Optional

pfdena

Specifies counter select. Only

available for Arria II GX,

Stratix III, and Cyclone III devices

onwards.

Optional

phasecounterselect[]

Specifies dynamic phase shifting.

Only available for Arria II GX,

Stratix III, and Cyclone III devices

onwards.

Optional

phasestep

Specifies dynamic phase

adjustment up or down. Only

available for Arria II GX,

Stratix III, and Cyclone III devices

onwards.

Optional

phaseupdown

The PLL enable port. When the

pllena

port is asserted, the PLL

drives out a signal, and vice versa.

When the

pllena

port is re-

asserted, the PLL has to re-lock.

All PLLs on the device share the

same

pllena

port.

Optional

pllena

Asynchronous clear port for the

real-time programming scan

chain, or the serial scan chain.

Only available for Stratix and

Stratix GX devices.

Optional

scanaclr

Input clock port for the serial scan

chain. Not available for Cyclone

and Cyclone II devices.

Optional

scanclk

(6)

Replace brackets, [], in the port name with integer to get the exact name. For example,

inclk0

,

inclk1

,

c1_

ena

, and

e0_ena

.

ALTPLL (Phase-Locked Loop) IP Core User Guide

Altera Corporation

ug-altpll

ALTPLL Input Ports

40

2014.08.18