Parameter setting, Operation modes – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 3

Parameter Setting

You select the PLL type on the General/Modes page of the ALTPLL parameter editor. The list of available

PLL types to choose from depends on the selected device family. If you select Select the PLL type

automatically, the ALTPLL parameter editor selects the best possible PLL type, based on other options that

you set in the ALTPLL parameter editor.

Related Information

•

Determining the PLL Lock Range

on page 6

•

on page 6

•

on page 9

•

on page 38

Total Number of PLL Available in Each Supported Device Family

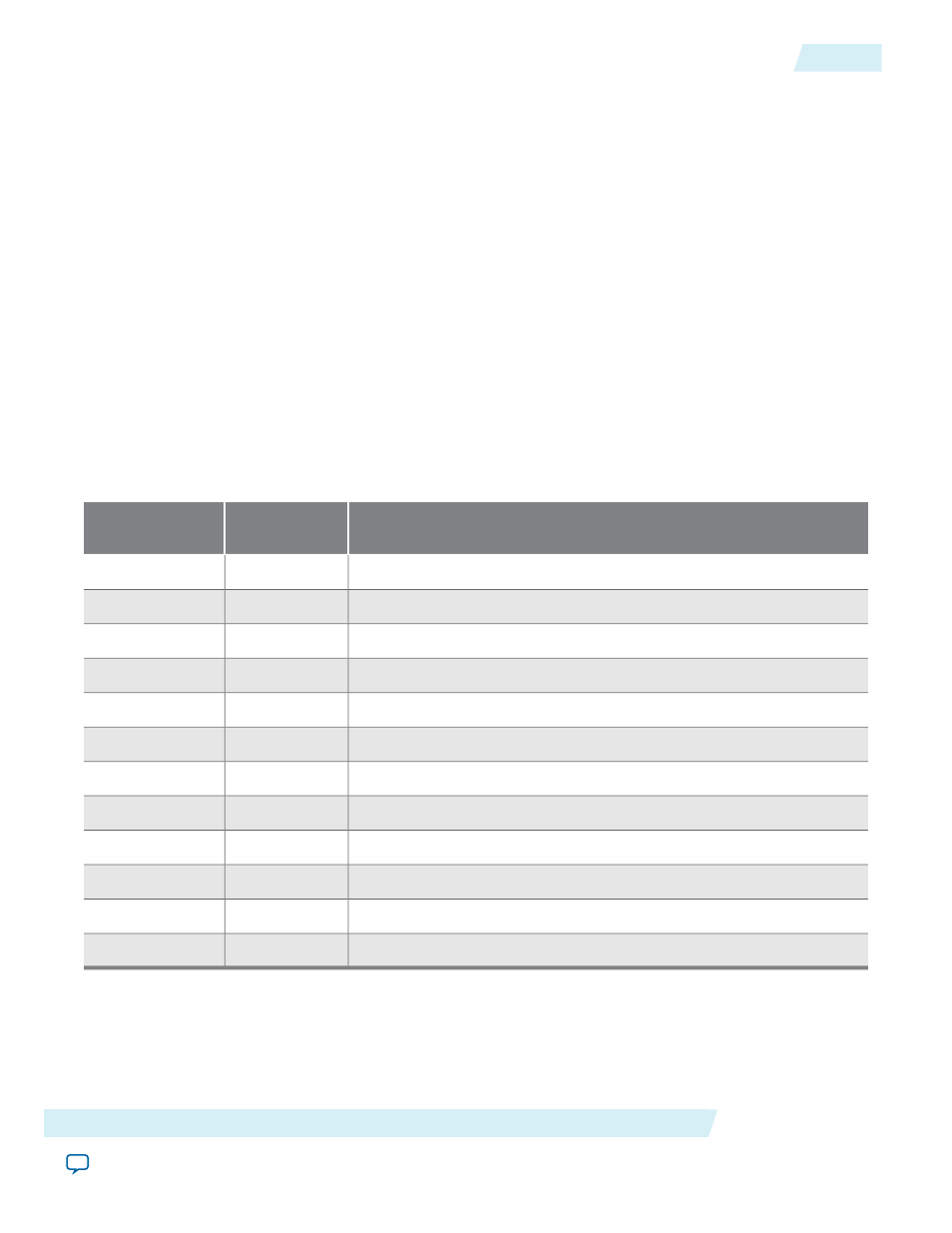

The following table lists the total number of PLLs available for configuration and the PLL types supported

by the ALTPLL IP core for each device family.

Table 1: Total Number of PLLs per Device Family

PLL Types

Total Number of

PLLs

Device Family

Enhanced and Fast

8

Arria GX

Left_Right

6

Arria II GX

Top_Bottom and Left_Right

12

Stratix IV

Top_Bottom and Left_Right

12

Stratix III

Enhanced and Fast

12

Stratix II

Enhanced and Fast

8

Stratix II GX

Enhanced and Fast

12

Stratix

Enhanced and Fast

8

Stratix GX

Cyclone IV PLL

4

Cyclone IV

Cyclone III PLL

4

Cyclone III

Cyclone II PLL

4

Cyclone II

Cyclone PLL

2

Cyclone

Operation Modes

The ALTPLL IP core supports up to five different clock feedback modes, depending on the selected device

family. Each mode allows clock multiplication and division, phase shifting, and duty-cycle programming.

Altera Corporation

ALTPLL (Phase-Locked Loop) IP Core User Guide

3

Parameter Setting

ug-altpll

2014.08.18