Implementing the ddr_clk design – Altera ALTPLL (Phase-Locked Loop) IP Core User Manual

Page 63

16. Turn on Use this clock.

17. Turn on Enter output clock parameters, and in the Clock multiplication factor box, type

5

.

18. In the Clock division factor box, type

1

.

19. In the Clock duty cycle (%) box, type

50.00

.

20. Click Next.

21. On page 14, repeat

through

for extclk e1.

22. Click Next.

23. On page 15, repeat

through

for extclk e2.

24. Click Next.

25. On page 16, repeat

through

for extclk e3.

26. Click Next. Page 17 appears. No input is required for this page.

27. Click Next. Page 18 appears.

28. On page 18, ensure that the Text Design File (.tdf), Pin Planner File (.ppf), AHDL Include File (.inc),

Block Symbol File (.bsf), and Sample waveforms in summary file (.html and .jpg) are turned on.

29. Click Finish. The ddr_pll module is built.

30. In the Symbol dialog box of the .bdf file, click OK.

31. Move the pointer to place the ddr_pll symbol between the input and output ports in the ddr_clk.bdf

file, connecting the inputs and outputs to the symbol. Click to place the symbol.

32. Save the design.

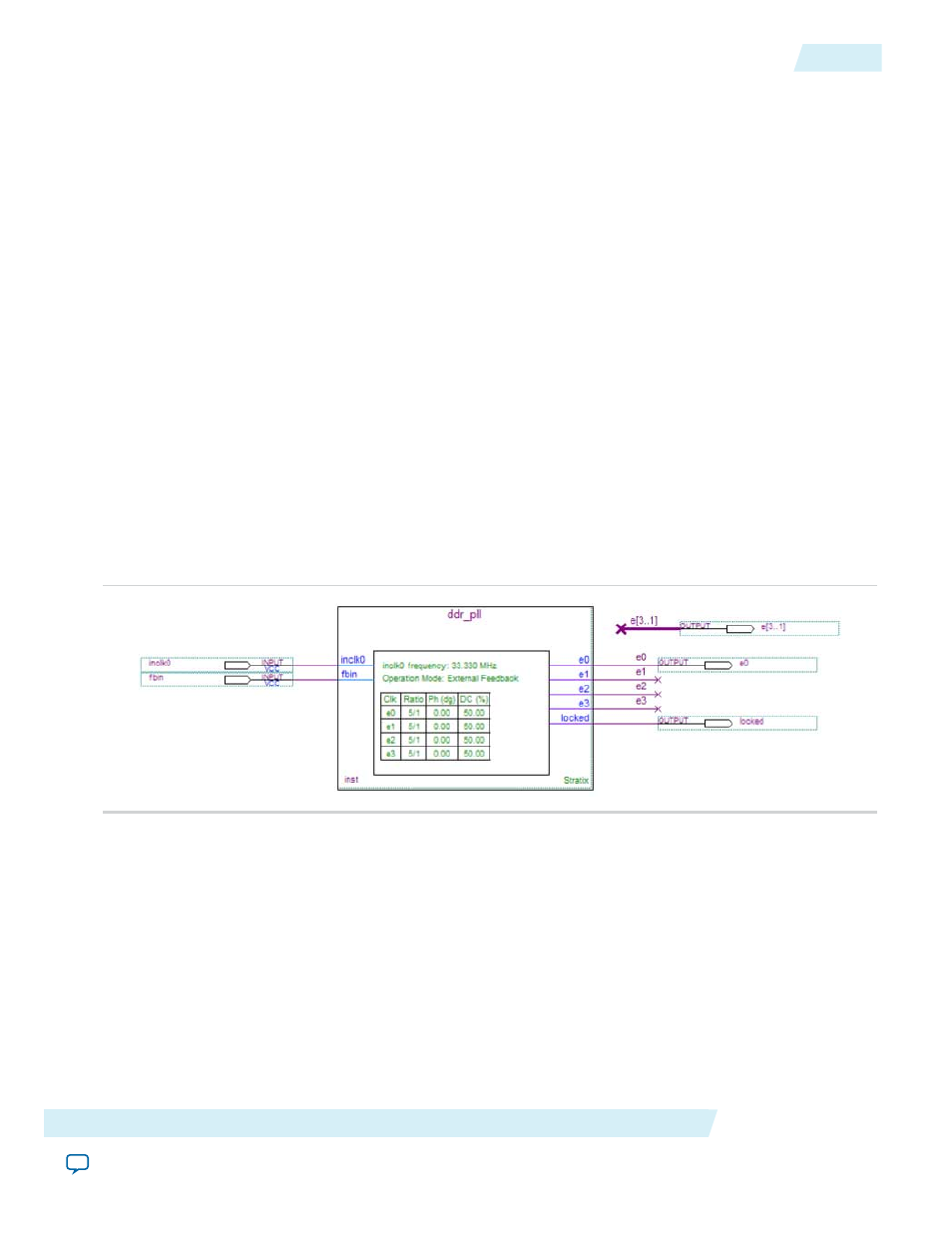

The following figure shows a completed design file.

Figure 28: ALTPLL ddr_pll Design Schematic

Implementing the ddr_clk Design

To assign the EP1S10F780 device to the project and compile the project, follow these steps:

1. On the Assignments menu, click Settings. The Settings dialog box appears.

2. In the Category list, click Device. Select Stratix in the Device Family field.

3. In the Target device section, under Available devices, select EP1S10F780C5.

4. Click OK.

5. On the Processing menu, click Start Compilation.

6. When the Full Compilation was successful message box appears, click OK.

7. To view how the module is implemented in the Stratix device, on the Assignments menu, click Timing

Closure Floorplan.

Altera Corporation

ALTPLL (Phase-Locked Loop) IP Core User Guide

63

Implementing the ddr_clk Design

ug-altpll

2014.08.18