Altera DisplayPort MegaCore Function User Manual

Page 123

Reset: 0×00000000

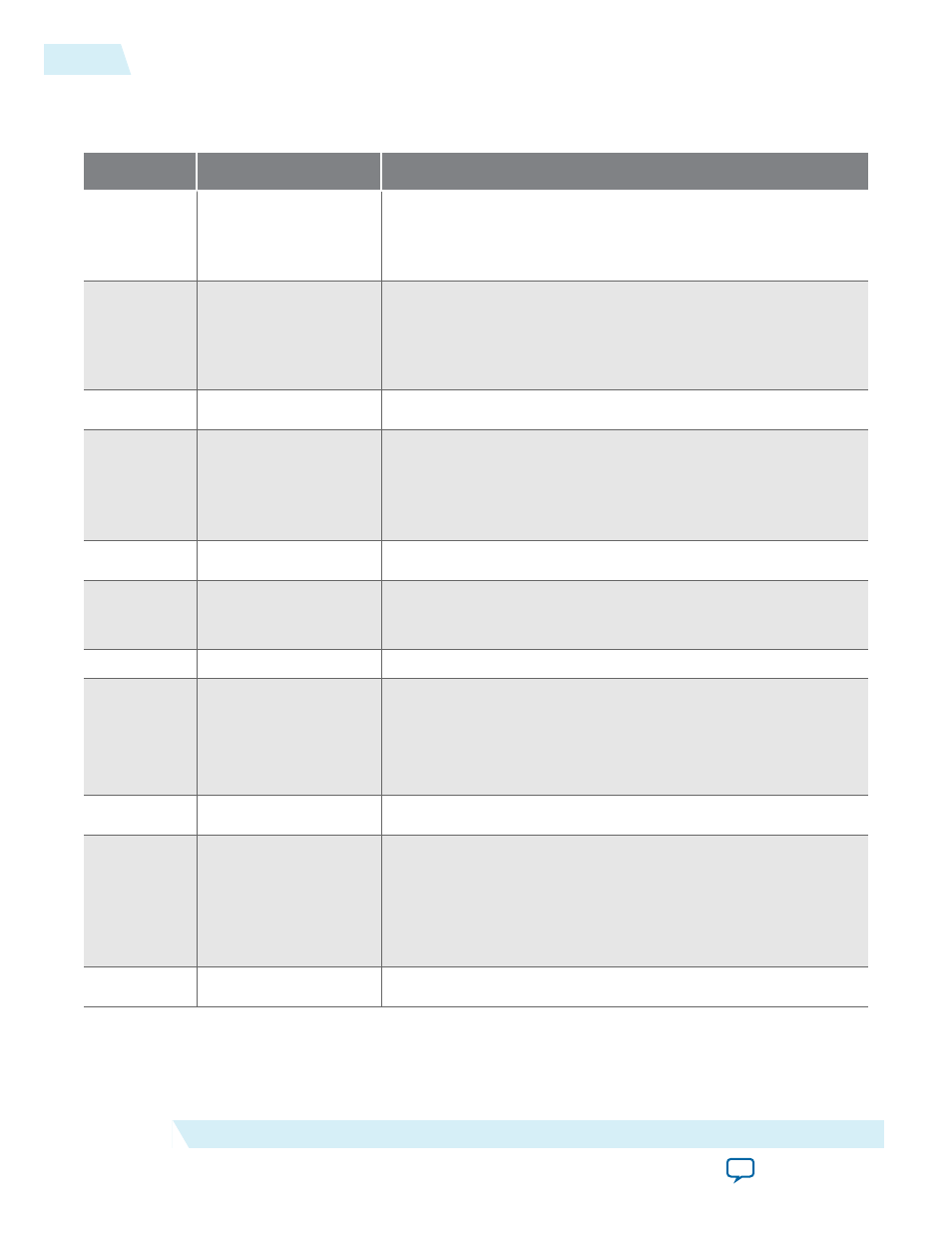

Table 9-2: DPTX_TX_CONTROL Bits

Bit

Bit Name

Function

31

HPD_IRQ_EN

Enables an IRQ issued to the Nios II processor on an HPD event:

• 0 = disable

• 1 = enable

30

AUX_IRQ_EN

Enables an IRQ issued to the Nios II processor when an AUX

channel transaction reply is received from the sink:

• 0 = disable

• 1 = enable

29

Unused

28:21

TX_LINK_RATE

Main link rate expressed as multiples of 270 Mbps:

• 0×06 = 1.62 Gbps

• 0×0a = 2.7 Gbps

• 0×14 = 5.4 Gbps

20

Reserved

Reserved

19

ENHANCED_FRAME

0 = Standard framing

1 = Enhanced framing

18:15

Unused

14

ASYNC_CLOCK

0 = Synchronous (reserved for future use)

1 = Asynchronous

Note: The core only supports asynchronous clock mode for

14.1 release. The register bit is always set to 1.

13:10

Unused

9:5

LANE_COUNT

Lane count:

• 00000 = Reserved

• 00001 = 1

• 00010 = 2

• 00100 = 4

4

Unused

9-2

DPTX_TX_CONTROL

UG-01131

2015.05.04

Altera Corporation

DisplayPort Source Register Map and DPCD Locations