Figure 6-1: hardware demonstration overview – Altera DisplayPort MegaCore Function User Manual

Page 63

Advertising

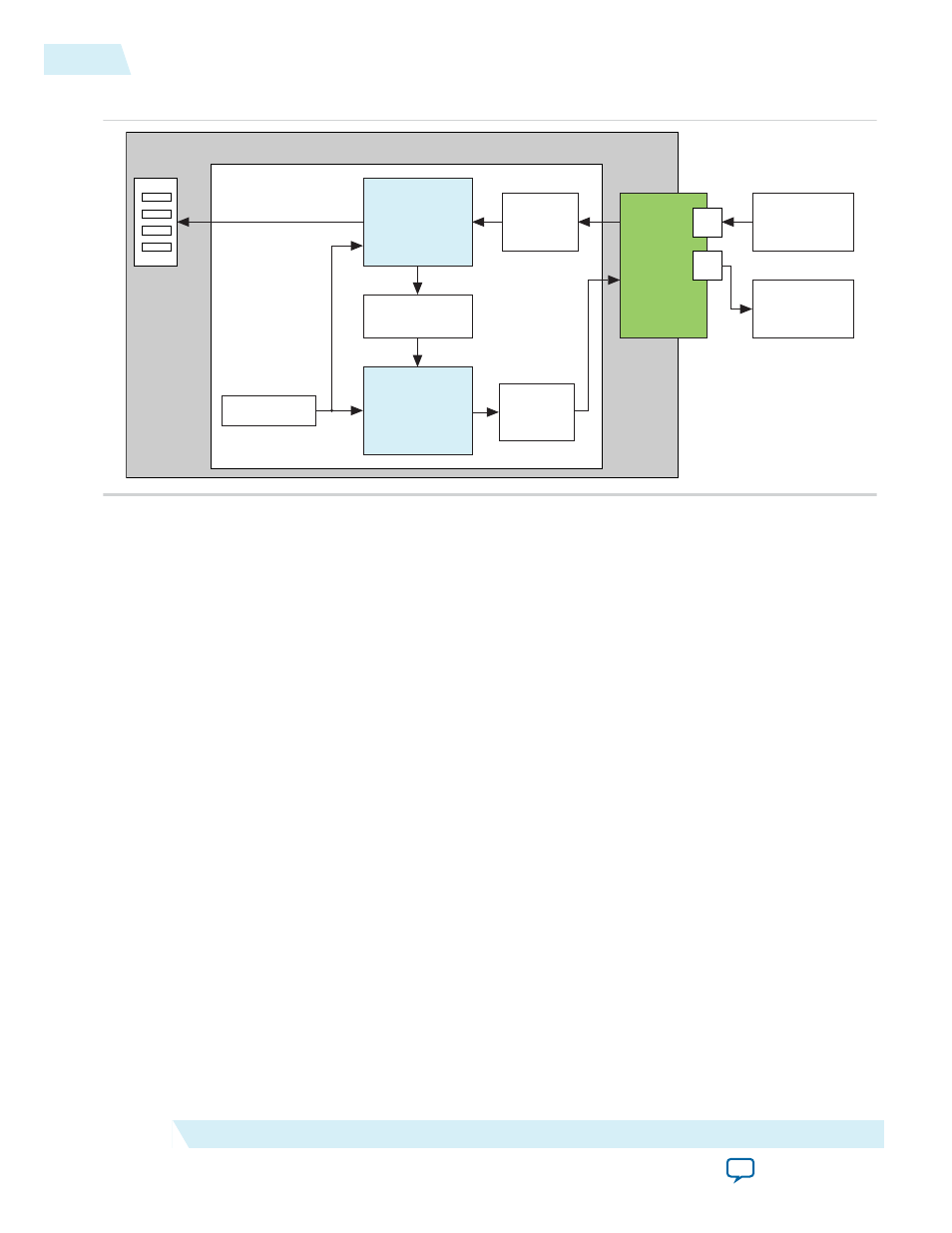

Figure 6-1: Hardware Demonstration Overview

DisplayPort IP Core

(Source)

Clock

Recovery

DisplayPort IP Core

(Sink)

User LEDs

RX

TX

Bitec HSMC

DisplayPort

Daughter Card

FPGA

FPGA Development Board

Nios II Processor

DisplayPort Source

(nVidia, ATI)

DisplayPort-Enabled

Display

Transceiver

Native PHY

(TX)

Transceiver

Native PHY

(RX)

The DisplayPort sink uses its internal state machine to negotiate link training upon power up. A Nios II

embedded processor performs the source link management; software performs the link training

management.

6-2

DisplayPort IP Core Hardware Demonstration

UG-01131

2015.05.04

Altera Corporation

DisplayPort IP Core Hardware Demonstration

Advertising