Altera DisplayPort MegaCore Function User Manual

Page 68

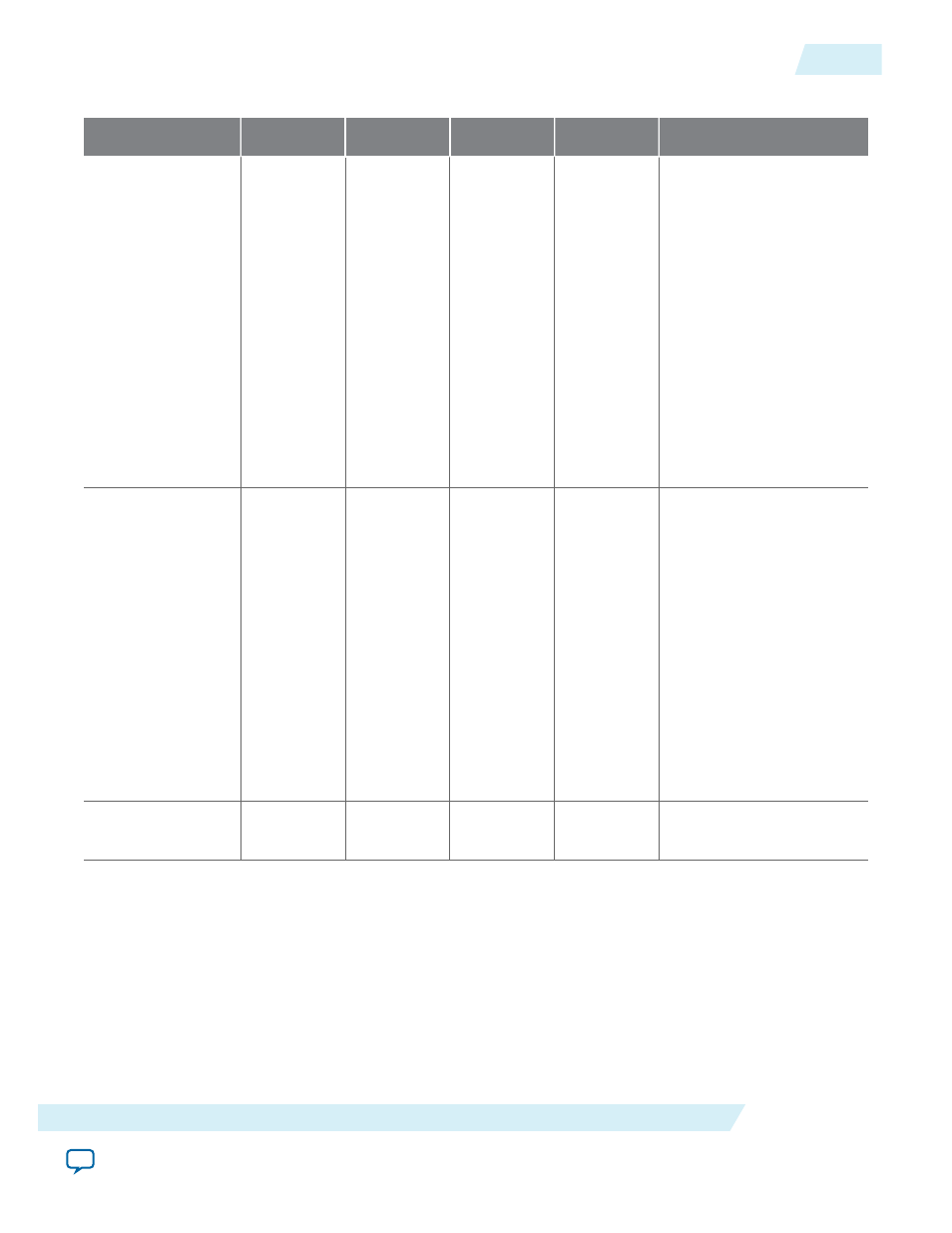

Table 6-3: Clock Recovery Interface Signals

Interface

Port Type

Clock Domain

Port

Direction

Description

control clock

Clock

N/A

clk

Input

Control logic clock. This

clock runs the loop

controller and fPLL

reconfiguration related

blocks.

Note: Altera

recommends

that you set

about 60 MHz

to achieve

timing

closure. Set

the CLK_

PERIOD_NS

parameter

accordingly.

RX link clock

Clock

N/A

rx_link_clk

Input

DisplayPort transceiver

link clock. This clock is a

divided version of the RX

main link clock. , or

divided by 4.

• Divided by 2 when

the sink core is

instantiated in 20-bit

mode (2 symbols per

clock)

• Divided by 4 when

the sink core is

instantiated in 40-bit

mode (4 symbols per

clock)

reset

Reset

clk

areset

Input

Asynchronous reset. This

is an active-high signal.

UG-01131

2015.05.04

Clock Recovery Interface

6-7

DisplayPort IP Core Hardware Demonstration

Altera Corporation