Edid interface, Debugging interface, Link parameters interface – Altera DisplayPort MegaCore Function User Manual

Page 50: Video stream out interface, Debugging interface -14

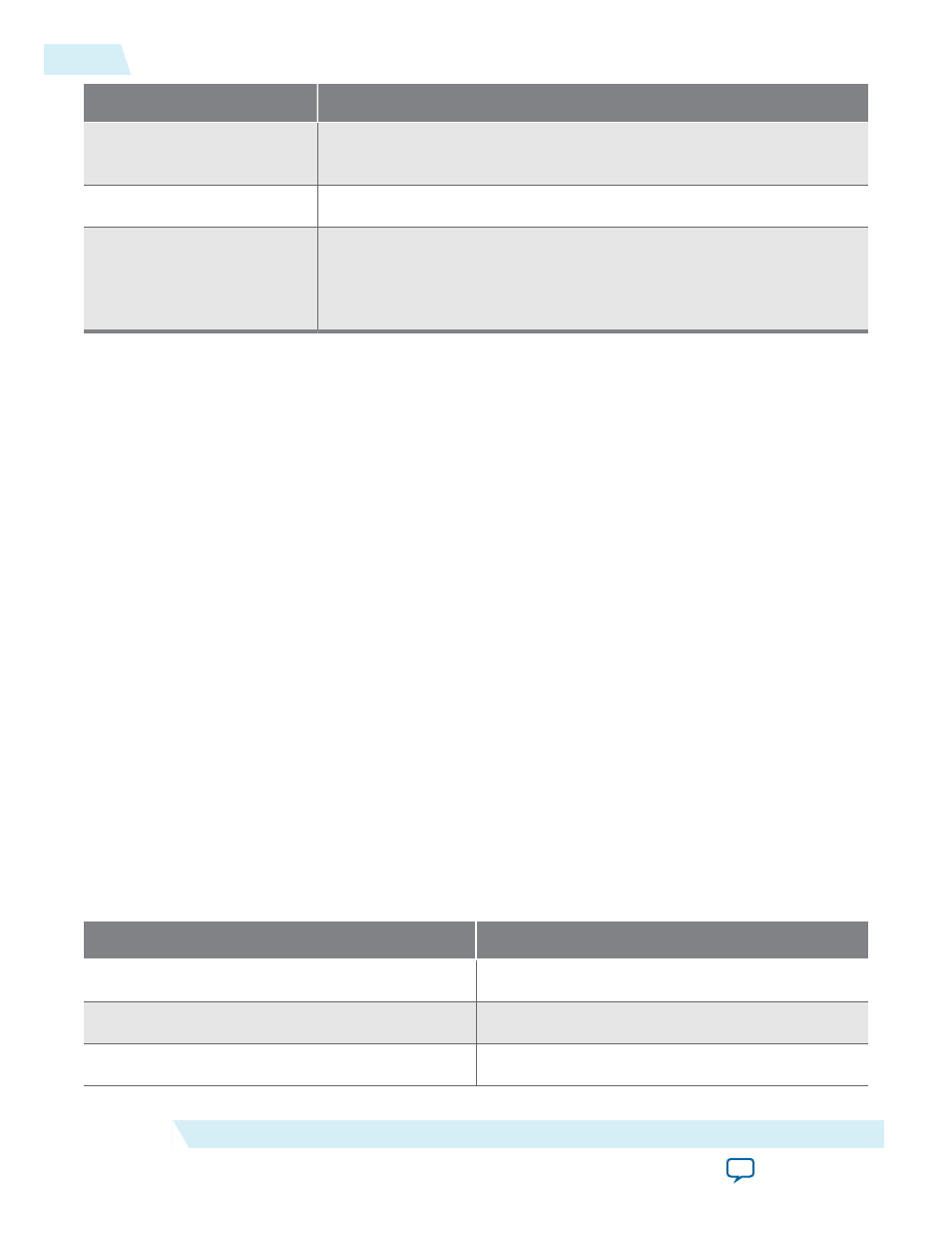

Port

Comments

rx_aux_debug_eop

Indicates the message packet’s last byte. The last byte should be ignored

and is not part of the message.

rx_aux_debug_err

Indicates if the core detects an error in the current byte.

rx_aux_debug_cha

Indicates the direction of the current byte.

1 = byte transmitted by the source.

0 = byte received from the sink.

EDID Interface

You can use the Avalon-MM EDID interface to access an on-chip memory region containing the sink’s

EDID data. The AUX sink controller reads and writes to this memory region according to traffic on the

AUX channel.

The Avalon-MM interface uses an 8-bit address with an 8-bit data bus. The interface assumes a read

latency of 1.

Note: The IP core does not instantiate this interface if your design uses a controller to control the sink;

for instance when you turn on the Enable GPU control parameter.

Refer to the VESA Enhanced Extended Display Identification Data Implementation Guide for more

information.

Debugging Interface

Link Parameters Interface

The sink provides link level data for debugging and configuring external components using the

rx_lane_count

port.

Video Stream Out Interface

This interface provides access to the post-scrambler DisplayPort data, which is useful for low-level

debugging source equipment. The 8-bit symbols received are organized as shown in the following tables,

where n increases with time (at each main link clock cycle, by 2 for dual-symbol mode or by 4 for quad-

symbol mode).

Table 5-11: rxN_stream_data Dual-Symbol Mode

Bit

Comments

63:56

Lane 3 symbol n + 1

55:48

Lane 3 symbol n

47:40

Lane 2 symbol n + 1

5-14

EDID Interface

UG-01131

2015.05.04

Altera Corporation

DisplayPort Sink