Dptx_mst_tavg_ts, Source aux controller interface, Dptx_aux_control – Altera DisplayPort MegaCore Function User Manual

Page 141: Dptx_mst_tavg_ts -20, Source aux controller interface -20, Dptx_aux_control -20

DPTX_MST_TAVG_TS

Target Average Timeslots

Address: 0×00aa

Direction: RW

Reset: 0×40404040

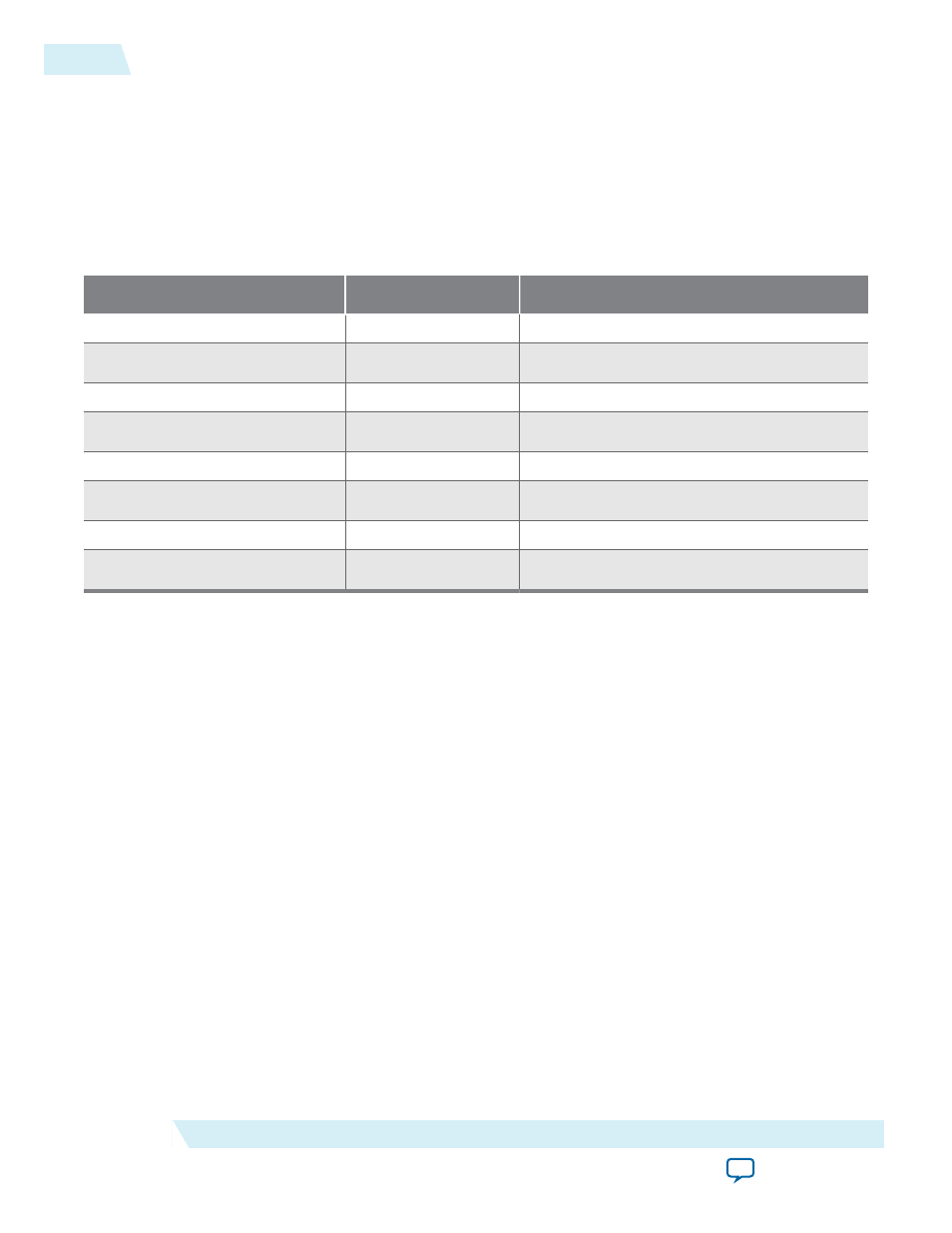

Table 9-38: DPTX_MST_TAVG_TS Bits

Bit

Bit Name

Function

31

Unused

30:24

TAVG_TS3

Target Average Timeslots for Stream 3

23

Unused

22:16

TAVG_TS2

Target Average Timeslots for Stream 2

15

Unused

14:8

TAVG_TS1

Target Average Timeslots for Stream 1

7

Unused

6:0

TAVG_TS0

Target Average Timeslots for Stream 0

TAVG_TS

x is expressed as the fractional part of the number of timeslots per MTU occupied by Stream x

times 64; assuming the allocated timeslots are the ceiling of this number. For example, if 4.7

timeslots/MTU are occupied (5 timeslots/MTU are allocated in the VCP ID table.

TAVG_TS

x = CEIL (FRAC (4.7)*64) = CEIL (0.7*64) = 45

The achieved precision for Target Average Timeslots regulation is 1/64 = 0.015625.

If

TAVG_TS

x is set to a value greater than 63, VCP fill is sent to each allocated timeslot.

Source AUX Controller Interface

This section describes the registers that connect with the AUX controller interface.

DPTX_AUX_CONTROL

For transaction requests:

1. Wait for

READY_TO_TX

to be 1.

2. Write registers

DPTX_AUX_COMMAND

to

DPTX_AUX_BYTE18

with the transaction command, address,

length (0 – 15) fields, and data payload.

3. Write

LENGTH

with the transaction’s total message length (3 for header + 1 for length byte + 0 to 16 for

data bytes).

4. The request transmission begins.

9-20

DPTX_MST_TAVG_TS

UG-01131

2015.05.04

Altera Corporation

DisplayPort Source Register Map and DPCD Locations