Build the fpga design, Load, and run the software, Build the fpga design -25 – Altera DisplayPort MegaCore Function User Manual

Page 86: Load, and run the software -25

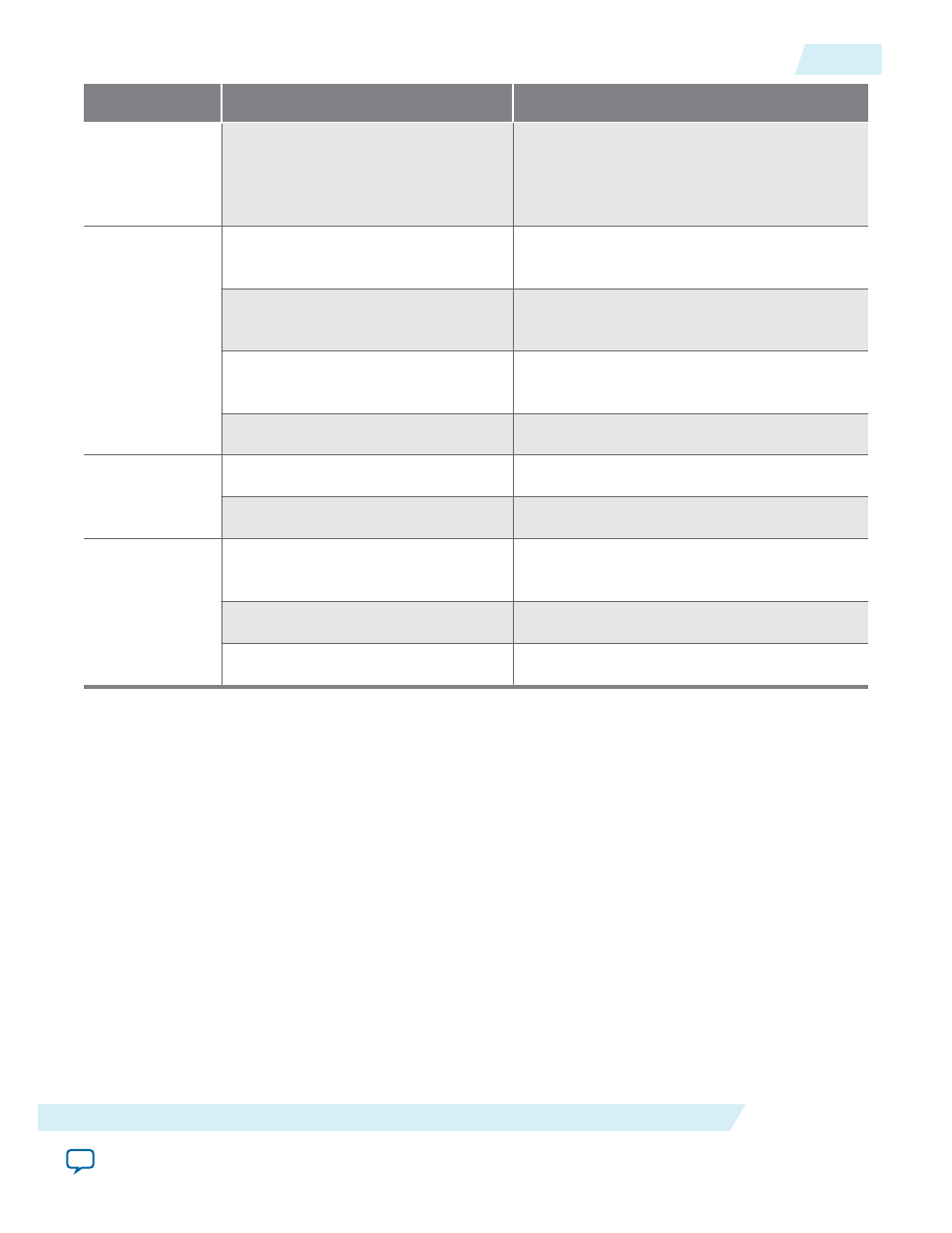

File Type

File

Description

Quartus II IP

files

bitec_reconfig_alt_

<prefix>

.qip

bitec_clkrec_dist.qip

bitec_clkrec.qip

Quartus II IP files that list the required

submodule files.

Scripts

runall.tcl

Script to set up the project, generate the IP and

Qsys system, and compile.

assignments.tcl

Top-level TCL file to create the project

assignments.

build_ip.tcl

TCL file to build the DisplayPort example

design IP blocks.

build_sw.sh

Script to compile the software.

Miscellaneous

example.sdc

Top-level SDC file.

bitec_clkrec.sdc

Clock recovery core SDC file.

Software files

(in the

software

directory)

dp_demo_src\

Directory containing the example application

source code.

btc_dprx_syslib\

System library for the RX API.

btc_dptx_syslib\

System library for the TX API.

Build the FPGA Design

In this step, you use a script to build and compile the FPGA design. Type the command:

./runall.tcl

This script basically builds the IPs and software, as well as performs Quartus full compilation.

Load, and Run the Software

In this step you load the software into the device, and run the software.

1. In a Windows Command Prompt, navigate to the hardware demonstration software directory.

2. Launch a Nios II command shell. You can launch it using several methods, for example, from the

Windows task bar or within the Qsys system.

3. From within the Nios II command shell execute the following command to program the device,

download the Nios II program, and launch a debug terminal:

nios2-configure-sof <project_name>.sof <USB cable number>; nios2-terminal

<USB cable

number>

UG-01131

2015.05.04

Build the FPGA Design

6-25

DisplayPort IP Core Hardware Demonstration

Altera Corporation