Dprx_aux_status, Dprx_aux_status -23 – Altera DisplayPort MegaCore Function User Manual

Page 174

The sink asserts the IRQ when

AUX_IRQ_EN

= 1 and

MSG_READY

= 1. To deassert IRQ, set

AUX_IRQ_EN

to 0

or read from

DPRX_AUX_COMMAND

.

Address: 0×0100

Direction: RW

Reset: 0×00000000

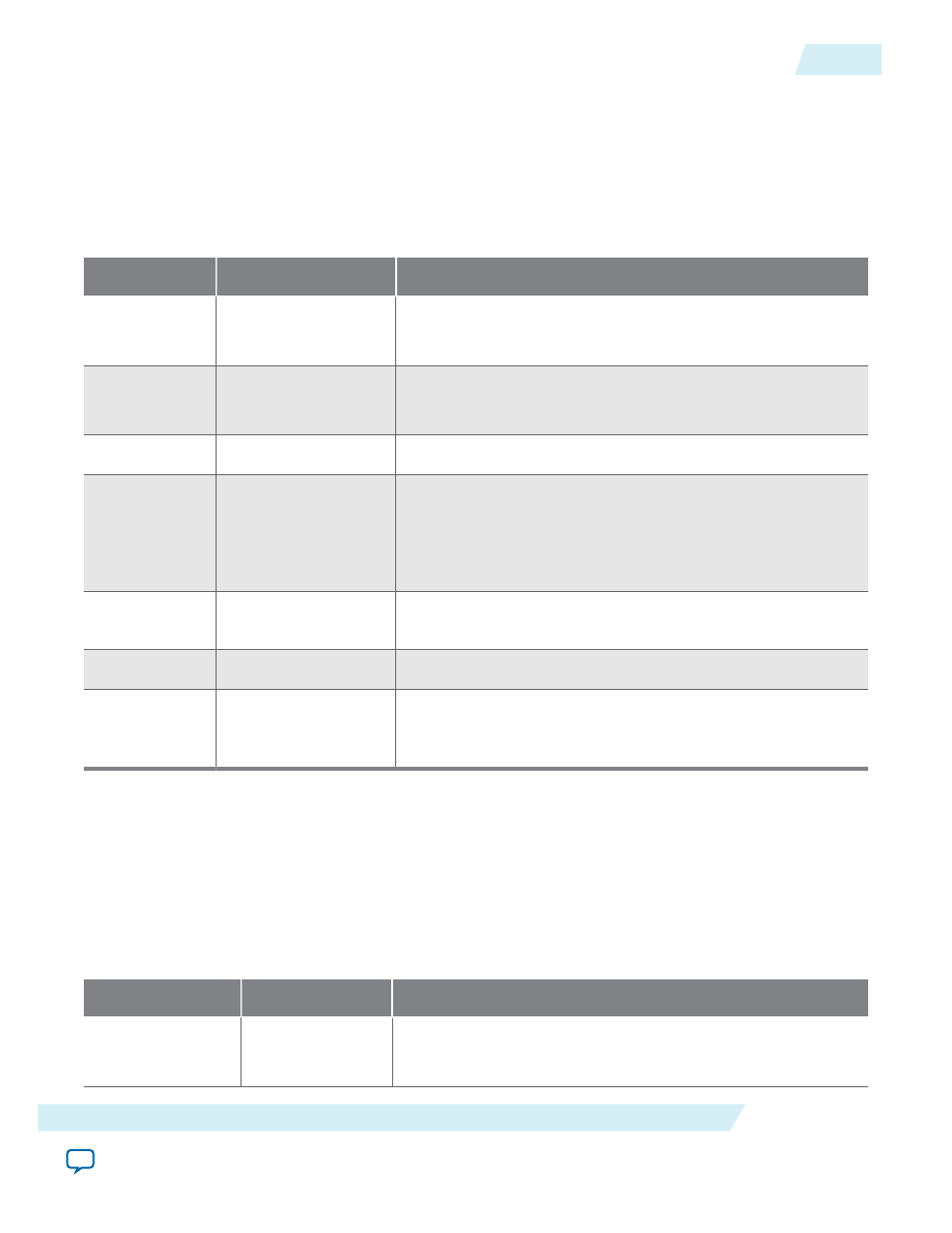

Table 10-42: DPRX_AUX_CONTROL Bits

Bit

Bit Name

Function

31

MSG_READY

0 = Waiting for a request

1 = A request has been completely received

30

READY_TO_TX

0 = Busy sending a reply or request waiting

1 = Ready to send a reply

29:9

Unused

8

AUX_IRQ_EN

Issues an IRQ to Nios II processor when the sink receives an

AUX channel transaction from the source.

0 = Disable

1 = Enable

7

TX_STROBE

Writing this bit at 1 starts a reply transmission. Always read this

bit as 0.

6:5

Unused

4:0

LENGTH

For the next transaction reply, total length of message to be

transmitted (1 – 17), for the last received transaction request,

total length of message received (1 – 17).

DPRX_AUX_STATUS

AUX transaction status register,

DPRX_AUX_STATUS

.

Address: 0×0101

Direction: RO

Reset: 0×00000000

Table 10-43: DPRX_AUX_STATUS Bits

Bit

Bit Name

Function

31

MSG_READY

0 = Waiting for a request

1 = Receives a request

UG-01131

2015.05.04

DPRX_AUX_STATUS

10-23

DisplayPort Sink Register Map and DPCD Locations

Altera Corporation